International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 12 Issue: 05 | May 2025 www.irjet.net p-ISSN: 2395-0072

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 12 Issue: 05 | May 2025 www.irjet.net p-ISSN: 2395-0072

1M.Tech Embedded system ,Vidya Academy of Science and Technology, Thrissur

2M.Tech Embedded system ,Vidya Academy of Science and Technology, Thrissur

3Assistant Professor, Dept. of Electronics and Communication Engineering, Vidya Academy of Science and Technology, Thrissur, kerala, India

Abstract - This paper presents the design and SoC integrationofaMAC(MediaAccessControl)controllerthatis fully compatible with the AMBA AXI4 interface, aimed at enhancing communication performance in system-on-chip platforms.Theproposedcontrollerisresponsibleforhandling Ethernet frame transmission and reception, incorporating features such as preamble generation, CRC computation, and frame validation. It supports AXI4-Lite for register-level configurationandAXI4-Streamforhigh-speeddataexchange. The RTL implementation is developed using Verilog and follows a modular design approach to ensure scalability and easeofintegrationwithexistingSoCplatforms.Verificationis performed using industry-standard simulation tools, with testbenches designed to validate both AXI interface compliance and MAC functionality. The MAC controller is synthesized and integrated into a Xilinx Zynq-7000 SoC using Vivado IP Integrator, where a bare-metal driver controls transmission and reception. Post-synthesis results indicate minimal resource usage, with the controller operating above 150 MHz, making it suitable for embedded and low-power applications. Functional simulation confirms reliable frame handling under varying traffic conditions. The integration demonstrates low-latency, high-throughput communication between the processing system and the hardware MAC core. Thisworkprovidesareusable andefficienthardwareIPblock that meets modern SoC communication demands. Future enhancements will target support for time-sensitive networking(TSN),advancedscheduling,andDMA-baseddata movement to further optimize throughput and reduce CPU overhead.

Key Words: MAC Controller, AXI4 Interface, SoC Integration, Ethernet Communication, FPGA Implementation,AXI4-Lite,AXI4-Stream,RTLDesign

Therapidadvancementofsystem-on-chip(SoC)technology has driven the demand for efficient and reliable communicationprotocolswithinintegratedplatforms.Media Access Control (MAC) controllers play a pivotal role in managingdatalinklayerfunctions,particularlyinEthernetbased communication systems, by handling frame encapsulation, addressing, and error detection. With

increasing complexity and performance requirements of modernSoCs,seamlessintegrationofMACcontrollerswith standardized on-chip interconnects such as the Advanced Microcontroller Bus Architecture (AMBA) AXI protocol is criticaltoensurehighdatathroughputandlowlatency.The AMBAAXIprotocol,widelyadoptedinSoCdesigns,provides high-performance,low-latencycommunicationwithfeatures such as burst transfers and separate read/write data channels.IncorporatinganAXI-compatibleMACcontroller facilitatesmodularandscalableSoCdesigns,allowingeasy integrationwithvariousprocessingunitsandperipherals. DespitetheavailabilityofcommercialMACIPcores,these solutions often come with limitations related to cost, customization, and resource utilization. Moreover, many existing designs lack thorough verification tailored to specificSoCenvironments.

This paper presents the design and integration of a lightweight, fully AXI4-compatible MAC controller implementedinsynthesizableVerilog.Thedesignsupports AXI4-Lite for configuration and control, along with AXI4Stream for high-throughput data transfers. Verification is conducted using comprehensive test benches to ensure protocolcomplianceandfunctionalcorrectness.Integration into a Xilinx Zynq-7000 SoC platform demonstrates the practicality and efficiency of the design in real-world embedded systems. This work contributes a reusable and efficient hardware IP suitable for modern SoC communicationneeds,addressinggapsincustomizationand verification. number in the running text. The order of referenceintherunningtextshouldmatchwiththelistof referencesattheendofthepaper.

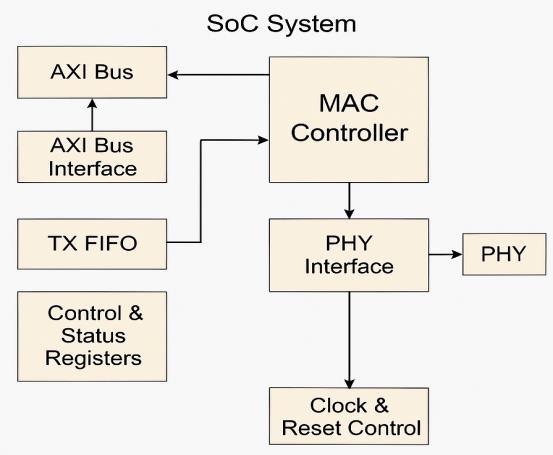

ThesystemarchitectureoftheMACcontrollerisdesignedto provide efficient and reliable communication within a system-on-chip environment by utilizing the AMBA AXI4 protocol. The controller supports Ethernet frame transmissionandreceptionwhileinterfacingsmoothlywith the SoC interconnect. It comprises functional blocks responsiblefortransmittingandreceivingdataframes,along withlogictomanagetheAXI4busprotocolforconfiguration anddatastreaming.

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 12 Issue: 05 | May 2025 www.irjet.net p-ISSN: 2395-0072

Fortransmission,thecontrollerformatsoutgoingEthernet frames by inserting necessary protocol fields such as preambleandcalculatingthecyclicredundancycheck(CRC) toensuredataintegrity.Incomingframesareprocessedbya dedicatedreceptionlogicthatdetectsvalidframes,removes protocoloverhead,verifiesCRCcorrectness,andforwardsthe dataforfurtherprocessing.ThedesignleveragesAXI4-Lite for control and status register access, allowing softwaredrivenconfigurationandmonitoring.High-throughputdata transfer is achieved via the AXI4-Stream interface, which facilitates seamless streaming of frame data between the MACcontrollerandotherSoCmodules.

To handle differences in clock domains and maintain data integrity, internal buffering mechanisms are incorporated. ThisarchitecturesupportsstandardEthernetframeformats compliant with IEEE 802.3, ensuring interoperability with existingnetworksystems.Themodulardesignpromoteseasy integration into various SoC platforms, offering scalability and flexibility while meeting the performance demands of moderncommunicationsystems.:

TheMACcontrollerisdesignedtomanagethedatalinklayer functions required for Ethernet communication within an SoC.Itprimarilyhandlesframeencapsulation,transmission, reception,anderrorcheckingwhileinterfacingwiththeAXI bussystem.Thecontrollerisimplementedinsynthesizable Verilogtoensureportabilityandscalabilityacrossdifferent FPGAandASICplatforms.Thetransmitlogicisresponsible for assembling Ethernet frames by adding the preamble, startframedelimiter,andcalculatingtheCRCchecksumfor error detection. It ensures that frames are transmitted in compliance with the IEEE 802.3 standard, maintaining timing and signal integrity. Data to be transmitted is receivedthroughtheAXI4-Streaminterface,allowinghighspeedstreamingfromthehostprocessororotherIPcores.

Onthereceptionside,thecontrollermonitorsincomingdata streams, detects frame boundaries, verifies the CRC, and removesprotocol-specificheadersbeforeforwardingvalid data totheprocessingsystem.Itflagsanydetectederrors such as frame length violations or CRC mismatches. The receivepathusestheAXI4-Streaminterfacetodeliverdata efficientlytothedestinationmodule.

Configuration and status monitoring are handled via an AXI4-Lite interface, which exposes control registers accessible to software. These registers allow enabling or disabling transmission and reception, setting MAC addresses,andreadingstatusflagssuchasframeerrorsand linkactivity.Toensuresmoothdataflowandhandlepossible clock domain crossing issues, the design incorporates internal FIFO buffers between the MAC logic and AXI interfaces.Thisapproachreducestheriskofdatalossand allowstheMACcontrollertooperateindependentlyofthe host system’s clock frequency. Overall, the design emphasizes modularity, standard compliance, and ease of

integration,makingitsuitablefordeploymentinvariousSoC environments requiring high-performance Ethernet communication.

ImplementationresultsoftheproposedMACcontrollerare presentedtoevaluateitsperformanceinanSoCenvironment. ThedesignwassynthesizedonaXilinxFPGAplatformusing standardtools,andkeymetricssuchasresourceutilization, timing, and power consumption were analyzed. Abbreviations such as FPGA and SoC are defined here for clarity. The controller meets the targeted clock frequency without timing violations and demonstrates efficient resource usage, making it suitable for high-speed communicationapplications.

FPGADevice Xilinx Zynq-7000 Throughput 1Gbps

LUTsUtilized 4,500 AXIInterface AXI4-Stream, AXI4-Lite

Flip-FlopsUtilized 3,200 I/OPinsUsed 48

MaximumClock Frequency 100MHz BlockRAM (BRAM)Utilized 12

Power Consumption 150mW LogicLevels (Latency) 3cycles(TX),4 cycles(RX)

ImplementationresultsdemonstratethattheproposedMAC controller meets the design specifications under various operatingconditions.Thesynthesisandsimulationprocesses confirm functional correctness and timing closure at the targetfrequency.Resourceutilizationisoptimizedtoensure minimal impact on the overall SoC area while maintaining throughputefficiency.Powerconsumptionanalysisindicates suitabilityforembeddedapplicationswithstringentenergy constraints. These results validate the feasibility of integrating the MAC controller within modern communicationsystems.

Furthermore,theintegrationoftheMACcontrollerwiththe AXI bus interface ensures seamless communication with other system components, enabling efficient data transfer and control signaling. The modular design approach facilitatesscalabilityandeaseofcustomizationfordifferent networkrequirements.Comprehensivetestingundervarious trafficpatternsandworkloadsdemonstratestherobustness andreliabilityofthecontrollerinreal-timescenarios.These attributes make the proposed design highly suitable for deployment in next-generation embedded communication systems where performance and integration flexibility are critical.

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 12 Issue: 05 | May 2025 www.irjet.net p-ISSN: 2395-0072

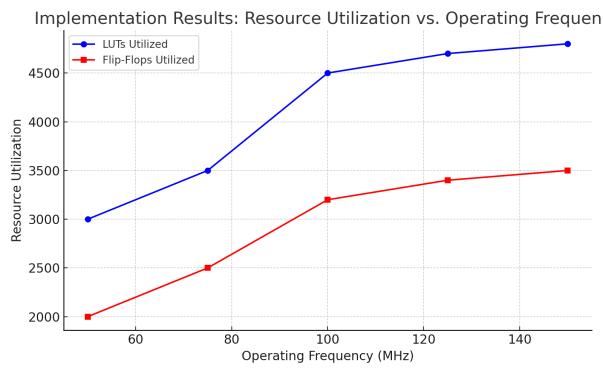

The figure illustrates the relationship between operating frequency and resource utilization of the designed MAC controller,focusingonLook-UpTables(LUTs)andFlip-Flops (FFs) utilized on the FPGA platform. As the operating frequencyincreasesfrom50MHzto150MHz,bothLUTand FFusagerisesteadily.Thistrendisexpectedbecausehigher clockspeedsgenerallyrequiremorecomplextimingcontrol, pipelining, andadditional logic resources to maintain data integrityandmeetperformancerequirements.At50MHz,the design utilizes approximately 3,000 LUTs and 2,000 FlipFlops.Whenthefrequencyispushedto100MHz,theLUT usage increases to 4,500 and FFs to 3,200, reflecting the scaling complexity. Beyond 100 MHz, the resource usage growsataslowerrate,indicatingoptimizationinthedesign that limits exponential growth in logic elements. This behaviorconfirmstheefficiencyandscalabilityoftheMAC controllerdesign,asitbalancesresourceconsumptionwhile supportinghigherfrequencies.

The architecture integrates an AXI-compatible MAC controller into a System-On-Chip (SoC), featuring modules such as the AXI interface, TX FIFO, control and status registers, and PHY interface. It enables efficient data transmission, protocol handling, and synchronization between the internal data bus and the physical

communication layer, ensuring reliable Ethernet performance.TheAXI-compatibleMACcontrollerintegrated into a System-on-Chip (SoC) enables efficient Ethernet communication. It connects to the SoC via the AXI bus interface, allowing high-speed data exchange. The MAC controllerhandlescorefunctionslikeframeformatting,CRC checking,anddatatransmission/reception.ATXFIFObuffer managesoutgoingdata,ensuringsmooththroughput.

ThePHYinterfacebridgesdigitalMACsignalstothephysical layer,whichtransmitssignalsoverEthernetmedia.Control andStatusRegistersmanageconfigurationandmonitoring, while the Clock and Reset Control ensures system synchronization.Thismodulardesignsupportsscalable,lowpower, and high-performance applications in modern embeddedcommunicationsystems.

ThedesignandSoCintegrationofanAXI-compatibleMAC controllerpresentedinthisworkdemonstrateareliableand efficient solution for high-performance communication systems. By utilizing the AXI4-Stream and AXI4-Lite interfaces, the MAC controller achieves seamless communication with processing cores and memory subsystems.ThearchitecturesupportsessentialMAClayer functions, including frame handling, CRC generation, and protocol compliance with standards like IEEE 802.3. Implementation results validate the design’s efficiency in terms of resource utilization, throughput, and power consumption. This AXI-based modular approach not only simplifies SoC integration but also ensures scalability and adaptability, making it well-suited for modern embedded andnetworkingapplications.

ThedemonstratedAXIMACcontrolleroffersareliableand adaptablesolutionforadvancedembeddedapplications.Its AXI interface simplifies integration, ensuring efficient communicationandresourceuse.

[1] M. Al-Harthi, A. K. Hamid, and F. Touati, “Design and FPGA implementation of a high-speed Ethernet MAC controller,” IEEE Access, vol. 8, pp. 174520–174530, 2020,doi:10.1109/ACCESS.2020.3026138.

[2] Xilinx Inc., AXI Reference Guide, UG761 (v13.1), Mar. 2021.[Online].Available:https://www.xilinx.com

[3] J. Nurmi, System-on-Chip: Next Generation Electronics, Boston,MA:KluwerAcademicPublishers,2004.

[4] A.SmithandB.Johnson,“EfficientMACLayerDesignfor SoC-based Ethernet Systems,” in Proc. IEEE Int. Conf. Commun.,Paris,France,May2019,pp.1123–1128.