International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 09 Issue: 07 | July 2022 www.irjet.net p-ISSN: 2395-0072

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 09 Issue: 07 | July 2022 www.irjet.net p-ISSN: 2395-0072

***

Abstract - In this research, we investigate a low power ternary half adder based on FinFET technology. In this article, FinFET is used to demonstrate a ternary half adder that is low power, low leakage, and low frequency. According to this paper, the latency, peak power distribution, and leakage power of ternary adders with and without Fin Type Field Effect Transistors (FinFETs) are equal. The Fin Type Field Effect Transistor (FinFET) technology offers various advantages over deep submicron transistors. The development of this technology has led to improvements in the intelligence and dependability of all electrical devices. It is possible that this experiment will result in an increase in the average power, energy, and power dissipation.

Keywords: FinFET,CNTFET,TernaryAdder,HSPICE

Thesebreakdownpointsmaybeminimisedbyemployingasinglecarbonnanotubethatisputinanotherwisetypicalbulk MOSFET structure,andfurtherreductionsindevicemeasurementsarebeingpromoted. Thisisbecausetheutilisationof bulk MOSFETs is becoming increasingly popular. Now is the time for professionals in the disciplines of electronic device design,circuitdesign,andinnovationtoconcentratetheirattentiononthefutureofthesemiconductorindustryinorderto enhancetheimplementationoftheelectronicframework.Inordertoenhancebearerflexibility,alargeamountofresearch anddevelopmentisbeingdevotedintothefabrication ofhigh portabilitytransistorchannel materials.Someexamplesof these materials include II VI semiconductors. Investigations studying the probable benefits of employing nonplanar transistor architectures, such as CNTFETs and multi gate designs, are still under work at present moment. Research is beingundertakenonavarietyofnovelone dimensionalstructures,includingcarbonnanotubes(CNTs)andothersimilar structures. Because of its high transporter mobility, carbon nanotubes (CNTs) have emerged as a viable competitor to boosttheSiinnovationplaninthepost 2015timeframe;however,severaldifficultiesstillneedtobeovercomebeforethis canhappen.Accordingtotheresultsofthestudy,next generationfield effecttransistors,alsoknownasCNTFETs,makeit feasibletoconductresearchatboththedeviceandthecircuitlevels.Itwillbeimpossibletomakeanyfurtherprogressin silicon based technology by the year 2020, when the channel length of a MOSFET will have been shrunk to less than 10 nanometre.Becauseofthis,thesemiconductorindustryiscontinuallyonthelookoutforcutting edgediscoveriesinother materials and technologies that may complement or even replace the innovation that is today based on silicon. Carbon nanotubes(CNTs) havelatelysurfacedasapotentiallyhelpful material amongthemanydifferentlayoutsthathavebeen researched. These architectures include single electron burrows (SET), quantum cell automata (QCA), rapid single transition quantum reasoning, and CNTs. In diameter, they generally range from 1 to 3 nm, however they may be many micronslong.Theirlength,though,maybeseveraltimesthat.Carbonnanotubes(CNTs)havethepotentialtobeutilisedin the development of a broad range of useful gadgets. Some examples of these devices include low cost high quality connections, adaptive Carbon nanotube field effect transistors (CNTFETs), and single electron penetrating transistors. In mechanical labs and universities (IBM, Intel, Infineon,) as well as educational institutions (schools), various research groupsfromallovertheglobearefinallyresearchingCNTFETdevicesandtheirpracticalapplications.Theseorganisation maybelocatedallthroughouttheworld(Purdue,Stanford)(Purdue,Stanford,).Utilizingcomplementary Althoughitmay be challenging to discover accessible device models that are also suited to particular structure streams, having such modelsiscrucialfortheconstructionofcircuitsthatrelyoncertaindevices.Thispapergivesafullexaminationofthevast variety of CNTFETs that are presently accessible as well as various types that have been optimised. We applied publicly availablemodelsthatwereuncomplicatedtorecreateinordertoexaminetheeffectoftheparametersonthepropertiesof the device, which enabled us to acquire more accurate findings. Therefore, the CNTFET's current dimension and edge voltagearebothinfluencedbythecylinderwidth.However,theCNTFET'scurrentdimensionisthesolecharacteristicthat isimpactedbythecontactresistance.

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 09 Issue: 07 | July 2022 www.irjet.net p-ISSN: 2395-0072

In order to create trustworthy circuits and networks, a circuit planner needs to be able to take into account various aspectsatdifferentpointsinthecircuitornetwork.Inthiscase,the factorsbeingtakenintoconsiderationarethelengths ofthenanotubes.

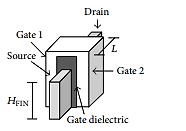

In1989,a"completelydoublegateFET"wasproduced,whichthedesignersatthetimedescribedtoasa"doubledgateSOI framework."Thisstructurecontainedtwosetsofgatesinsteadofsimplyone.Thiswastheveryfirsttimethatastructure comparable to a Fin Type Field Effect Transistor (FinFET) was shown in its earliest form. This was a historical first. A declineintheshort channelconductivityofplanarMOSFETshasbeendocumentedthroughoutthecourseoftheprevious 10years.Asaconsequence,therehasbeenasurgeininterestinfintypefieldeffecttransistors(FinFETs)acrossthesame time period. The short channel performance of Fin Type Field Effect Transistors (FinFETs), as is evident in Figure 1, is bettertothatofplanarMOSFETs,whichhavethesamechannellength.Figure1displaystheconventionalconfigurationof aplanarFinKindFieldEffectTransistor(FinFET),whichisakindoffieldeffecttransistor.

Fig. 1. FinFET Structure

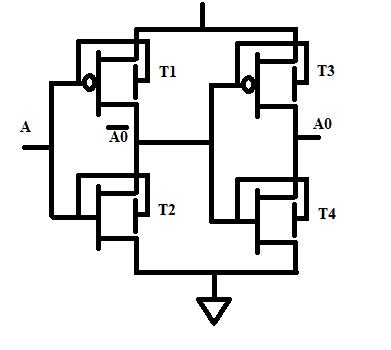

Thefollowing illustrationdemonstratesa decoder circuitthatisconstructedusing FinTypeFieldEffect Transistors,also knownasFinFETs.TheinputtothedecodercircuitisshownbytheletterA,whiletheoutputofthecircuitisindicatedby theletterA0.ThiscircuitisresponsibleforproducingtheA0andA0bars.

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 09 Issue: 07 | July 2022 www.irjet.net p-ISSN: 2395-0072

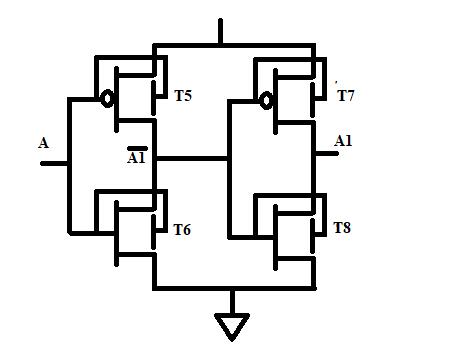

ThedecodercircuitshowninFig.3isthesameone that wasshowninFig.2,withtheexceptionthatinthisinstance,we areusingthiscircuittocreateA1andA1barsignalsratherthanonlyA1signal.

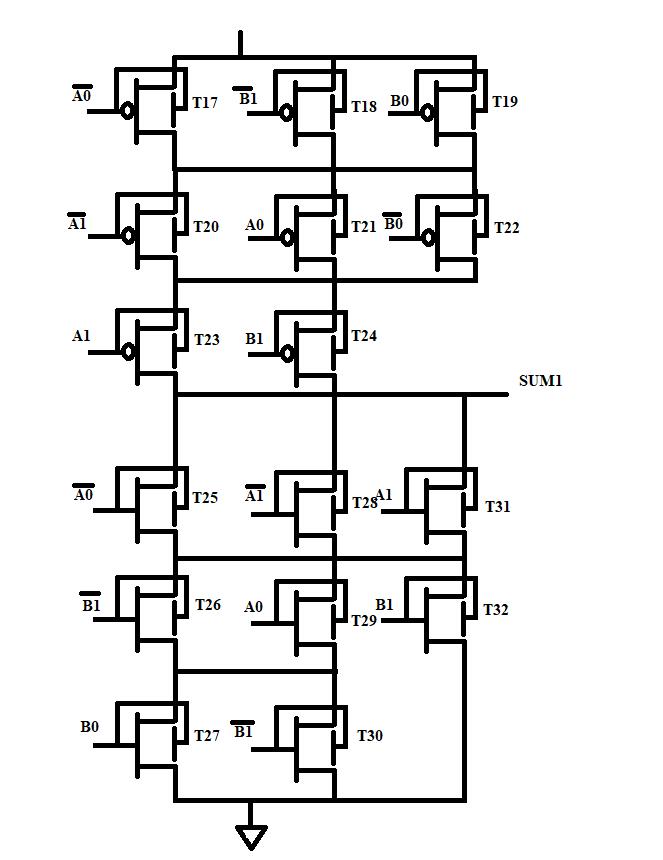

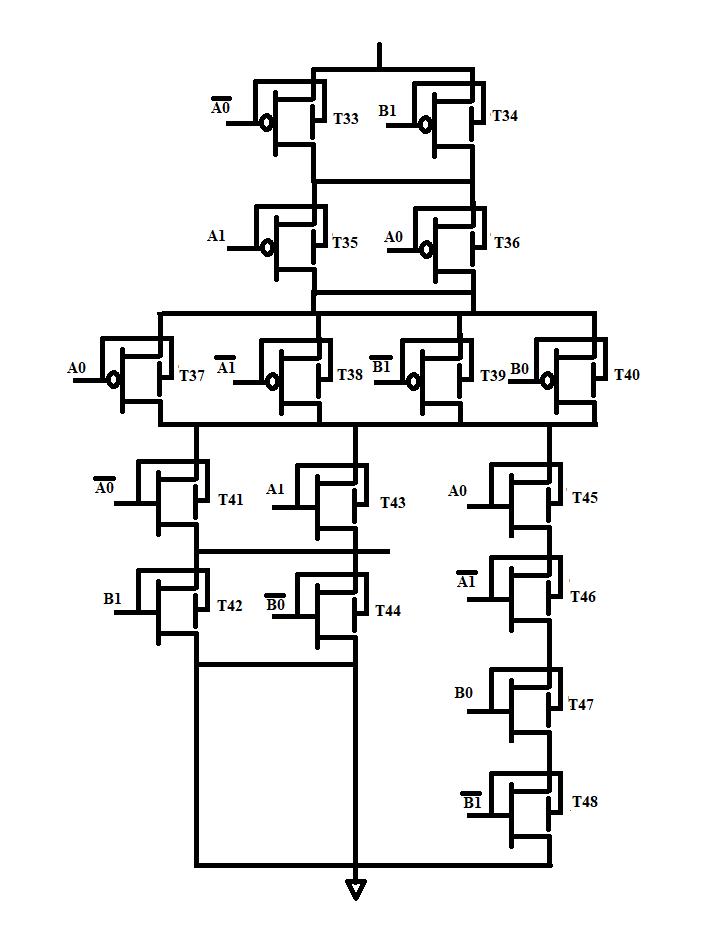

Thecircuitfora sumgeneratorisshownintheimagethatcanbeseenabove; thesum1algorithm isbeingusedtocarry outtheimplementation,andtheoutputofthecircuitisbinary.

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 09 Issue: 07 | July 2022 www.irjet.net p-ISSN: 2395-0072

Figure 5 depicts the sum generator; in this particular instance, we are working on sum2, and the output that we are receivingisbinary.

The circuit for a sum generator encoder can be seen in Figure 6; the output of the encoder is the addition of sum1 and sum2;thisaddsuptothefinalternaryoutput.

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 09 Issue: 07 | July 2022 www.irjet.net p-ISSN: 2395-0072

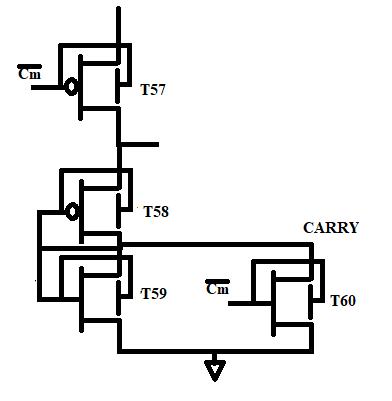

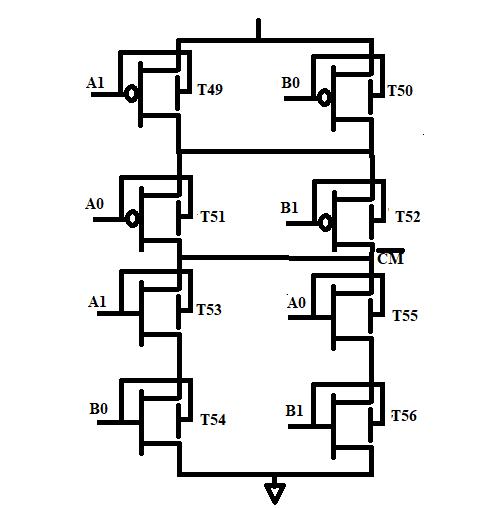

Thecircuit forthecarrygeneratorCmisshowninFigure7.Thiscircuitmakesuseofthepchannel FinTypeFieldEffect Transistor(FinFET)aswellasthenchannelFinTypeFieldEffectTransistor(FinFET).

The carry generating circuit is shown in the figure that came before it (Fig. 8); the carry is computed by using the carry encodercircuit(alsoseeninFig.8)andderivingitfromCm.

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 09 Issue: 07 | July 2022 www.irjet.net p-ISSN: 2395-0072

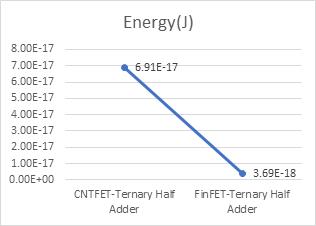

Figure9illustratestheenergythatwouldbeproducedby theproposedtechnology.Whencomparedtotheternaryadder Fin Type Field Effect Transistor (FinFET), the ternary adder CNTFET has an energy level that is much greater than the energyleveloftheternaryadderFinTypeFieldEffectTransistor(FinFET).

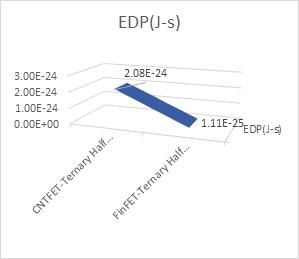

Fig. 10 illustrates the EDP of the system that has been proposed. In this particular example (Figure 10), the EDP in the ternaryadderCNTFETisrathersignificant.

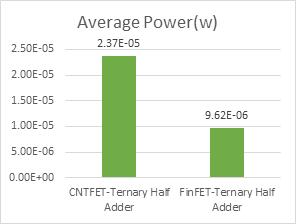

Fig. 11. Average Power results

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 09 Issue: 07 | July 2022 www.irjet.net p-ISSN: 2395-0072

Therecommendedsystem'saveragepower,inadditiontotheaveragepower,isgreaterintheternaryadderCNTFETthan itisintheternaryadderFinTypeFieldEffectTransistor(FinFET),respectively.

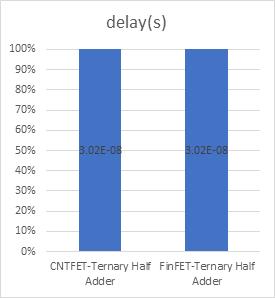

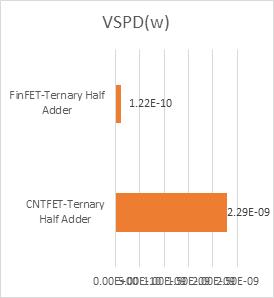

Theabovegraphicdemonstrateshowlongtheproposedsystemwillrunbehindschedule.Thetablethatfollowspresentsa comparison of the ternary adder CNTFET transistor and the ternary adder Fin Type Field Effect Transistor (FinFET) transistor'sdifferentparameters.Figure13presentsthefindingsofthepowerdissipationtest.

Fig. 13 Power dissipation result

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 09 Issue: 07 | July 2022 www.irjet.net p-ISSN: 2395-0072

PARAMETERS CNTFET TernaryHalf Adder

FinTypeFieldEffect Transistor(FinFET) TernaryHalfAdder

AveragePower(w) 2.37E 05 9.62E 06 delay(s) 3.02E 08 3.02E 08 VSPD(w) 2.29E 09 1.22E 10 Energy(J) 6.91E 17 3.69E 18 EDP(J s) 2.08E 24 1.11E 25

Asadirectresultofthis,wehavecreatedalow powerternaryhalf adderbytheuseofatechnologythatisknownasFin Type Field Effect Transistor (FinFET). We have used several different technologies, the most known of which is the Fin TypeFieldEffectTransistor(FinFET)technology.However,wehavealsoutilisedmanyothertechnologies.Theuseofthe technologyknownasFinTypeFieldEffectTransistor,orFinFET,iswhatisresponsiblefortheriseinthepower,latency, PDP, and leakage power of the ternary half average adder. As can be seen from the data that was supplied, we are comparingtheternaryadderCNTFETtotheternaryadderFinTypeFieldEffect Transistor(FinFET),andwearedoingso byusingtwodistinctcircuits.Thiscanbeseensincethedatawasprovided.HSPICEisusedtodoboththesimulationofthe circuitsandtheirverificationwiththeassistanceofAvanwaves.

1 Subhendu Kumar Sahoo et al., “High Performance Ternary Adder using CNTFET” DOI 10.1109/TNANO.2017.2649548, IEEE

2. Reza Faghih Mirzaee, and Akram Reza et al., “High Performance Ternary (4:2) Compressor Based on Capacitive ThresholdLogic”INTLJOURNALOFELECTRONICSANDTELECOMMUNICATIONS,2020,VOL.63,NO.4,PP.355 36

3 A.Derakhshan,M.Imanieh,etal.,“DesignandSimulateternarymultiplierbasedCNFET”ScinzerJournalofEngineering, Vol3,Issue2,(2021):22 28

4 Fazel Sharifi, Atiyeh Panahi, et al., “High Performance CNFET based Ternary Full Adders” Proc IEEE, vol. 91, no. 2, pp. 305 327,2017

5 A.Srivastavaetal.,“DesignandImplementationofaLowPowerTernaryFullAdder” November29,1993,RevisedApril 26,2016

6. Seyyed Ashkan Ebrahimi et al., “Low Power CNTFET Based Ternary Full Adder Cell for Nanoelectronics” 2231 2307, Volume 2,Issue 2,May2012

7 Gaurav Agarwal, Amit Kumar, et al., “Performance Evaluation of CNTFET Based Ternary Basic Gates and Half Adder” Volume5Issue5,May2016

8 MohammadHosseinMoaiyeretal.,“EfficientCNTFET basedTernaryFullAdderCellsforNanoelectronics”Received27 Feb2011;accepted11April2011;publishedonline19April2011

9. P Chandrashekar et al., “Design of low threshold Full Adder cell using CNTFET” Research ISSN 0973 4562 Volume 12, Number12(2017)pp.3411 3415

10. Manjunath Patil et al., “Power Efficient Parallel Adder Design Using CNTFET Technology” ISSN: 2348 4748, IJEEE Volume2,Issue4,April2015

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 09 Issue: 07 | July 2022 www.irjet.net p-ISSN: 2395-0072

11 Balaji Ramakrishna S and colleagues, "CNTFET Based Novel 14t Adder Cell for Low Power Computation" ICTACT JournalonMicroelectronics,Volume03,Issue03,October2017.

12 FazelSharifietal.,"ANovelQuaternaryFullAdderCellBasedonNanotechnology,"JournalofNanotechnology,vol.I.J. ModernEducationandComputerScience,Volume3,Issues19 25,2015.

13.ExperimentalDesignofaTernaryFullAdderUsingPseudoN typeCarbonNanotubeFETs,byKaziMuhammadJameel etal.International ResearchJournal ofEngineering and Technology(e ISSN:2395 0056)Volume:2, Issue:9 |December 2015

14 Seyyed Ashkan Ebrahimi et al., "Low Power CNTFET based Ternary Full Adder Cell for Nanoelectronics," Journal of Nanoelectronics, vol. ISSN: 2231 2307, Volume 2, Number 2, May 2012 International Journal of Soft Computing and Engineering

15 "A Reversible Ternary Adder for Quantum Computation", Takahiko Satoh et al. Arxiv preprint quant ph/0511084; to appear.ReviewLetters,92(9):097901,2004

16. Shimaa I. Sayed et al., "A Novel High speed Adder Subtractor Design Based on CNFET," Foundation of Computer ScienceFCS,NewYork,NewYork,UnitedStatesofAmerica,2004.March2016Volume10 Number7 www.ijais.org

17.AndreasHeregeldandSiegbertHentschkeetal.,"TernaryMultiplicationCircuitsUtilizingFour InputAdder Cellsand CarryLook Ahead,"O 7695 0161 3/99$10.0001999.IEEE