International Research Journal of Engineering and Technology (IRJET)

Volume: 09 Issue: 07 | July 2022

Abstract

e-ISSN: 2395-0056

www.irjet.net p-ISSN: 2395-0072

Volume: 09 Issue: 07 | July 2022

Abstract

e-ISSN: 2395-0056

www.irjet.net p-ISSN: 2395-0072

Department of Computer Science and Engineering, RV College of Engineering Bengaluru, India.

Today’s mobile or wireless devices use System on Chips that are incorporated with reusable IP Cores so that they are easily adaptable to new technologies and specifications.Thispapergivesanoverviewofvariouson chip bus protocols such as Inter Integrated Circuit (I2C), Improved Inter Integrated Circuit (I3C), Peripheral Component Interconnect Express (PCIe), Serial Peripheral Interface (SPI) and Universal Asynchronous Receiver/Transmitter (UART), which are used by System on a Chips (SoCs) to communicate with the devices. This paper provides a brief overview and a survey of functioningorimplementationofbusprotocolsforvarious applicationsinaSystem on Chip.

AMBA, ASIC, FPGA, I2C, I3C, PCI, RTL, SoC, SPI, TDMA, UART,USB,VHDL

The process of decreasing the size of integrated circuits has become increasingly popular and important in the modern day. Because of user/customer demands, chip manufacturers are integrating more components to chipsets. These system on a chips or chipsets consist of one or more programmable components, such as application specific Intellectual Property (IP) cores, processor cores, or digital signal processors, on chip memory, front end and back end designs, input/ output devices,andothercircuitsspecificallydesignedforagiven application. And buses are a shared communication medium in Communication Architecture (CA) of an SoC that the devices utilise to communicate with one another. Thispaperfocusesonvariouson chipcommunicationbus protocols providing a survey of various protocols such as UART,I2C,SPI,PCIe,andI3C.

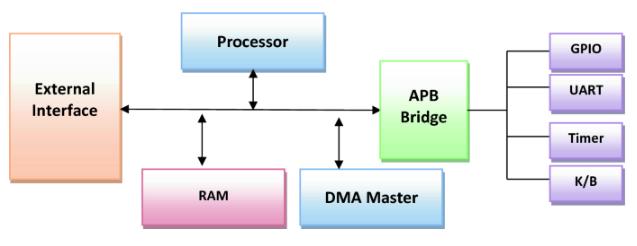

Fig. 1.1 Different bus protocols connected to processor

The above figure shows how different bus protocols can communicate with the SoC or processor using AHB APB busorAMBAbridge.

Currently,theprocessorandseveralsensors,likecameras and accelerometers, communicate using the I2C protocol. I2Cisaserialbusinterfacecommunicationprotocolthatis built into devices. Despite I2C's wider adoption over the years, it is still lacking key essential functionalities, which is a problem given how many sensors and other components mobile as well as mobile influenced systems are integrating. The I3C is a new serial communication interface specification that enhances the capabilities, efficiency, and power consumption of I2C while keeping backward compatibility with the majority of devices. I3C offers the simplicity, low pin count, flexible PCB design, and multi drop benefits of I2C while also offering the fasterdataratesof12.5MHzandreducedpowerofSPI.In Band Interrupts, efficient power management, Dynamic Addressing, , and Hot Join are then added by I3C, along withbetterthroughputforaspecificfrequency.

This section of the paper contains a survey of present technologies and research available related to the on chip bus protocols in an attempt to better understand the efforts that have gone into this field of study and also understand the implementation and applications of these bus protocols in SoC. The papers discussed in this section includeworkrelatedtoimplementationofI2CusingFPGA, VHDL,comparativestudiesofprotocolssuchasSPI,UART andreviewpapersonprotocolslikeUART,I2Cetc.

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 09 Issue: 07 | July 2022 www.irjet.net p-ISSN: 2395-0072

By automating the connections between components, plug and play designs can minimise the construction time for complicated systems. Although plug and play technologies have been successfully used in aerospace systems, their general adoption, especially in smaller satellites, is limited by the overhead of the interface electronics. Bryan Hansen discusses a straightforward plug and playinterfacein[1]thatisbasedonthepopular I2C standard and results in considerable optimizations of the interface circuits necessary to be plug and play compatible.Atitsmostfundamental,Mini PnP/SPA 1isan I2Cprotocoloverlaythatcanbesimplyimplementedusing hardware that already complies with this widely accepted standard.Networksofmini PnP/SPA 1devicescanlink to moretraditionalplug and playarchitecturesviagateways. TheSPA 1hardwareissimilartootherlegacyinterfacesin that it is simple to integrate into plug and play software andthatitsupportsessentialplug and playfunctionalities including electronic datasheets and automated enumeration. The development and demonstration of COTSandrad tolerantSPA 1interfacemoduleversions,as well as the present state of the global programme, are coveredinthispaper.

DmitryLevshun,AndreyChechulinandIgorKotenkoet.al [2]haveproposedamethodologyforensuringthesecurity and dependability of the data transfer environment in microcontroller based systems. The paper's main contribution is a new method for designing data transfer protocols that enables creating suggestions for enhancing the functionality of the data transfer protocols to satisfy the stated functional and non functional requirements. This approach provided the possibility to combine the main concepts of traditional methodologies and modify them to create a dependable and secure data transfer environment. The suggested method enables designers to create a secure and dependable data transmission environment in microcontroller based devices without enlisting security experts. This is made feasible by the automatic analysis of data transmission protocols and the formulation of suggestions for enhancing their functionality to satisfy the needs. The calibre of the used expert knowledge base directly affects the range of alternative options. This implies that the accuracy and applicability of this knowledge base directly influence the quality of the solutions that the technique offers. As a result,thisstrategycannotfullyreplaceexpertknowledge. By incorporating dynamic addressing, integrity control, message transmission with a size limit of 160 bytes, encryption, and mutual device authentication into the suggestedapproach,theintendedI2Cprotocol'scapability was enhanced above its simple implementation for Arduino devices. These modifications result in a 20

percent and a 60 percent drop in the planned I2C protocol's data transmission speed and message payload, respectively. An specialist in the security of microcontroller based systems, who is familiar with the best and most highly specialised solutions now available, will typically come up with more effective methods to createadependableandsecuredatatransferenvironment than the technique indicated. The recommended method, ontheotherhand,mightbehelpfultotheprofessionalasa toolforautomatingaportionofnormalchoresaswellasa source of answers that are different from their subjective opinion. Additionally, the created solution is a component oftheDLSEDSdesignapproachforsecuremicrocontroller basedsystems.

In the paper [3], author Ekta Patnaik, has focussed on the design of the I2C transport controller and the interface between the two coordinated devices, a microcontroller and an EEPROM, acting as a master controller and a slave for serial communication in a built in system. Just two bidirectionalwiresandacommonprotocolareusedasthe I2Ctransportcontroller'scomponentelementstotransmit data between two coordinated circuits and devices. Serial clocklinecomesinsecondaftertheserialinformationline. PhilipsSemiconductorscreatedtheI2Cstandardtoenable faster devices to communicate with slower devices and with one another without information loss. The entire moduleisdescribedinVHDL,andModel SIMsimulatesit.

The main element of a computer's serial communications subsystem is the UART controller. Bytes of data are taken and transmitted by the UART as sequential bits. SPI is a popular technology used nowadays for peripheral device communication when we need to transport data quickly andunderreal timelimitations.Forcounterstriggered by surface detectors, a subterranean data gathering system has been developed. It communicates with a dedicated processorusingtheUARTandSPIprotocols.M.Pooraniet. al [4], in their study, have implemented the entire system usingXilinx12.4iandSPARTAN3EFPGA.TheSPIprotocol is checked using a 12 bit DAC MCP4922, while the UART protocol ischeckedusinga hyper terminal.Thesuggested approachcanefficientlysupplybothprotocolsforwireless serial communication. These serial protocols are mostly utilisedbywirelesszigbeetechnology.

The commonly used serial data transmission technology UART supports full duplex connection. Depending on the applicationa designer needsUARTfor,therearea variety of methods it can be implemented. Some UARTs have FIFOs for the receiver or transmitter to use as a data buffer, while others operate in 9 bit mode, and so on. In this paper[5], Ashwini Dhanadravye and Samrat S Thorat

e-ISSN: 2395-0056

Volume: 09 Issue: 07 | July 2022 www.irjet.net p-ISSN: 2395-0072

have reviewed many methods that were used in conjunction with UART for secure data delivery. The receiver module, transmitter module, and baud rate generator are the three primary kernel modules in the UART design, and they all play a significant part in the serial communication between the UART and host CPU. The many techniques researchers have used to achieve serial communication through UART modules are presented in this study. Since Verilog Hardware Description Language makes the design implementation easiertoreadandcomprehendandcanbeintegratedinto the FPGA to deliver compact, stable, and reliable data transfer, the majority of researchers have utilised it to create the UART modules. Thus, the use of UART can be investigatedutilisingvariousalgorithmsandtechniquesto better and more effectively meet the communication demands. Particularly in the area of embedded systems, where SOC technology has recently gained prominence, thisarchitecturehasconsiderablesignificance.

In the paper [6], authors Poonam R Kedia and N. N. Mandaogadehavedemonstratedthecontroller'sstructure aswellasanapproachtodesigninganasynchronousFIFO. ThiscontrollerisbuiltwithaFIFOandUARTcircuitblock on an FPGA to quickly and efficiently integrate communication in contemporary complicated systems. Here, the UART basic operations are implemented using VHDL and integrated into an FPGA chip to achieve stable, dependable, and compact data transfer. They have concentrated on baud rate generation at various frequencies and check the received data for errors in the result and simulation section. The UART architecture includestheBaudRateGenerator.Accordingtotheneeds, this frequency divider will automatically adapt. A multi channelUARTcontrollercanalsobecreatedbasedonFIFO technology,FPGA,anditisalsosignificantforthedesignof SOC to meet the communication requirements of contemporarycomplicatedcontrolsystems.

Regu et al. [7] has focused on the interface between the master bus protocol and the slave using the I2C (inter integrated circuit) protocol. Here, the microcontroller is connectedtoaDS1307.TheDS1307receives8bitdatavia theI2Cbusprotocolfromthemicrocontroller.I2Cissized and powered for efficiency. Any high speed or low speed device,aswell asanylowspeedorhighspeeddevice,can use this principle. This module serves as a master for the microcontroller device, which can be viewed as a slave, whileservingasaslavefortheDS1307.Itcanconnectlow speed peripherals such as motherboards, embedded systems,mobilephones,set topboxes,DVDplayers,PDAs, andotherelectronicdevices.

Amandeep Kaur et. al [8] described a design of eUART (enhanced UART). The advantages of the eUART when used for real time communication are demonstrated in this paper, along with the approach's capabilities and limitations.InordertocommunicatewithaTTP/A(Time Triggered Protocol Class A) or LIN (Local Interconnect Network) network, this SPEAR processor's expansion modulewasdeveloped.Itiseconomicallyadvantageousto construct even low cost devices with a distributed microcontroller basedcontrolsystembecauseoftechnical advancesmadebythesiliconindustry.Afieldbusnetwork connectsmultiplesensorsandactuatorsinordertoobtain theinformationfromtheenvironment.Real timefunctions arefrequentlyrequiredsincesuchfield bus basedsystems are employed for controlling purposes. Two field bus protocols that meet the requirements are TTP/A and LIN. Both protocols strive to establish reliable communication while also reducing costs by utilising commercial off the shelf (COTS) hardware, such as common UARTs. It is preferabletocombineallcomponentsontoasingle silicon dieinordertoreducethesizeandcostofanetworknode. Since quartz crystals can't yet be incorporated on silicon dies, the clock source must either be used or put next to the chip, which increases size and cost. The low clock frequency prevents the UART's transmission rate from being adjusted, which causes an arithmetic error. Another issue is caused by the RC high oscillator's frequency drift, which has a direct impact on the UART's baud rate. In reality, it was determined that typical components cannot function under these circumstances by analysing the effects of an imprecise oscillator on a TDMA based network. The analysis' findings led to the development of theeUARTprototype.TheeUARTcanfunctioneveninthe worst case scenario by lowering the arithmetic error in baudratesettingandeliminatingthetransmitjitter.Thus, the message sender's synchronisation pattern enables the eUART to automatically synchronise its baud rate. The eUARTmodulealsohasafilterstatemachineandoffers I6 fold oversampling in order to increase the communication's reliability. It is possible to configure the sampleinterpretation to work bestfor defect detection or availability.

A way to construct UART communications based on programmable logic devices is suggested in this study [9] by Yongcheng Wang and Kefei Song, in order to link devices using asynchronous communications protocol to DSPswithsynchronousserialports.Thesuggestedmethod usesVHDLtoincorporatethebasicUARTcapabilitiesinto the CPLD. After analysing a few ways to actualize UART, the UART data frame format and operational principle were first introduced. In depth illustrations of the use of VHDLtoimplementUARTtransmitter,UARTreceiver,and

e-ISSN: 2395-0056

Volume: 09 Issue: 07 | July 2022 www.irjet.net p-ISSN: 2395-0072

baud rate generator were provided. Then the VHDL programme was pre simulated and synthesised. Finally, the physical system underwent the bit error rate test. According to experimental findings, UART utilises 75% of the GLB, and the bit error rate is less than 10 9. The RS 422 protocol was used to carry out the experiment, and the baud rate is 62.5 kb/s. The suggested approach can meet the system needs for high integration, stabilisation, lowbiterrorrate,potentanti jamming,andlowcost.

I2C and SPI are the most widely used serial protocols for both intra and inter chip low/medium bandwidth data transfers. Using numerous new Xilinx FPGA families, A.K. Oudjida et al [10] has analysed and compared the logical and physical aspects of the two protocols, emphasising which elements of the protocols are considerably increasingareaoverhead.Theutilisationofthisknowledge helps architects make well considered and precise decisions. I2C and SPI are both implemented as general purpose IP alternatives for a comprehensive comparison research, according to a recent market analysis of a considerable variety of commercial I2C and SPI devices. These systems offer every feature needed by contemporary ASIC/SoC applications. From the study, the authors found out that the I2C over SPI area overhead caused by the RTL code is about 25%, and the latency for the two systems are nearly the same. Although this comparison is only applicable to the slave side of the protocol, it is simple to make reasonable predictions for the master side: roughly the same latency with a larger area overhead to accommodate the I2C protocol's multi mastercapability.Ifastraightforwardcounter basedbaud rateisimplemented,therewon'tbeanyappreciablespace overhead for SPI Master compared to SPI Slave. If a digital frequencysynthesiserisutilisedinstead,thiswon't bethecase.TheresultsofamodernFPGAimplementation oftheslavesideofthetwocommonprotocolsI2C/SPIare alsopresentedinthepaper.

Fieldbus applications that are still commercially viable increasingly call for real time communication. The fieldbuses LIN and TTP/A provide a temporally deterministic communication protocol that uses a standard UART (Universal Asynchronous Receiver/Transmitter) as a communication interface in ordertotakethisrequirementintoconsideration.Because UARTs were not initially intended for this kind of application, issues can occur that increase the amount of softwareand processingrequired orlowerthe bandwidth that can be achieved. Martin Delvai and Ulrike Eisenmann et. al[11], in their study, have shown a UART module that has been used for real time applications. The described real time communication protocols call for periodic

synchronisation, which is made possible by a synchronisation mechanism that also lessens the complexity of the software. The UART can also initiate activities in response to happening events. In this approach, the UART module may handle a sizable portion of the communication process on its own. Both send jitter and arithmetic error associated with baud rate setting havebeentotallyeliminated.Asaresult,theUARTmodule canoperatewitherraticclocksourcesthathaveahighrate ofdrift,suchaslow costRCoscillators.

Junwei Zhou, Andrew Mason, et al. [12] have developed a new sensor bus for low power micro software systems, evaluated sensor network architectures, and analysed currentdigitalcommunicationbusesthatareoftenusedin sensornetworks.Inordertominimisehardwareoverhead at the sensor node, the new intra module multi element microsystem (IM2) bus is a nine line interface with 8b serial data that offers a number of cutting edge features likeplug and playandpowermanagement.Thediscussion has ended with a few wireless sensor networking related topics. The discussion of these topics offers recommendations for selecting the best bus for various sensornetworkapplications.IM2 preservesthebenefitsof bothIEEE1451.2TIIandI2Cbus,whereasIM2 isdesigned with short wiring distances between the microsystem module controller and the sensor nodes for low power microsystemapplications.

AhighspeedprotocolsuchasI3CisusedinOISorOptical Image Stabilisation System. OIS is used in today’s smartphones to improve mobile photography by physically adjusting the camera sensor or lens module to counterbalance any little camera movement to prevent blurryshots.Thissystemrequirescommunicationwiththe processor in very high frequency to send the data completely and thus I3C is used in this system. NFC is a collection of short range wireless technologies that normally require a connection to be established at a distance of 4 cm or less. Between an Android powered smartphone and an NFC tag or between two Android powered devices, NFC enables the sharing of tiny data payloads. These NFC applications use SPI or I2C to communicate with processors based on the specific applicationoftheNFC.

Nowadays, smartphones include a magnetometer that allowsustosensethedirection/orientationinspace.Some simple applications such as the Compass App can be used to locate oneself in relation to Magnetic North. Magnetometer uses I3C or I2C to communicate with the

e-ISSN: 2395-0056

Volume: 09 Issue: 07 | July 2022 www.irjet.net p-ISSN: 2395-0072

processor. Sensors such as IMU accelerometers, pressure sensors,humiditysensorsandsometouchsensorsuseI2C as the communication protocol in the current smartphones.2 wireand4 wireUARTsarewidelyusedby the low power bluetooth module. GPS receivers and GPRS modems also use UART for communication purposes. In display fingerprint sensors, mounted under the display of thesmartphones,useSPIastheircommunicationprotocol. SPI is also used by some 3rd party camera applications, Laser Range Finders and flicker detection modules. These are some of the important applications of various bus protocolsincurrentsmartphoneapplications.

Various on chip protocols are reviewed, along with their features,architecturesorapplications,inthispaper.There is a descriptive comparison of different on chip protocols. UART is an effective hardware communication protocol that uses asynchronous serial communication with configurablespeed.I2CProtocolisaserialcommunication method that allows variousdevices to exchange data with oneanother.Fordatatransmissionandreceptionbetween masters and slaves, it is a half duplex, bi directional and two wire bus system. Serial peripheral interfaces are widelyusedinmicrocontrollersandotherdevicessuchas sensors, ADCs, shift registers and others. It is a synchronous mode of communications where the devices aresynchronisedontherisingandfallingedgeoftheclock. ThesebusprotocolsarewidelyusedinSoCdesign,Sensor networking,andalltheseprotocolscanbeimplemented in FPGAusingVHDLandClanguage.

[1] Lyke, J., Mee, J.K., Bruhn, F., Chosson, G., Lindegren, R., Lofgren,H.,Schulte,J.,Cannon,S.R.,Christensen,J.,Hansen, B., Vick, R., Vera, A., & Calixte Rosengren, J. “A Plug and play Approach Based on the I2C Standard”. 24 th Annual AIAA/USU Conference on Small Satellites, SSC10 VII 7, 2019

[2] D. Levshun, A. Chechulin and I. Kotenko, "A technique for design of secure data transfer environment: Application for I2C protocol," 2018 IEEE Industrial Cyber PhysicalSystems(ICPS),2018,pp.789 794,

[3] Ekta Patnaik, Sachin Bandewar, “Design and Realization for Interfacing Two Integrated Devices Using I2C Bus a Review'', International Research Journal of Technology And Applied Science, 05 May 2017, pp. 186 195,doi:10.17005./IRJTAS.2017.0809001

[4] M. Poorani and R. Kurunjimalar, "Design implementation of UART and SPI in single FGPA," 2016 10th International Conference on Intelligent Systems and Control (ISCO), 03 November 2016, pp. 1 5, doi: 10.1109/ISCO.2016.7726983.

[5] Ashwini D Dhanadravye and Samrat S Thorat. “A Review on Implementation of UART using Different Techniques”. International Journal for Computer Science andInformationTechnology,10June2014,pp.394 396.

[6] B. Eswari, N. Ponmagal, K. Preethi and S. G. Sreejesh, "Implementation of I2C master bus controller on FPGA," International Conference on Communication and Signal Processing, 2013, pp. 1113 1116, doi: 10.1109/iccsp.2013.6577229.

[7]AmanpreetKaurandAmandeepKaur.“Anapproachfor designing a universal asynchronous receiver transmitter (UART)”. International Journal of Engineering Research and Applications (IJERA) ISSN: 2248 9622, Vol. 2, Issue 3, May Jun2012,pp.2305 2311

[8] Y. Wang and K. Song, "A new approach to realize UART," Proceedings of 2011 International Conference on Electronic & Mechanical Engineering and Information Technology, 2011, pp. 2749 2752, doi: 10.1109/EMEIT.2011.6023602.

[10] A.K. Oudjida, M.L. Berrandjia, R. Tiar, A. Liacha, K. Tahraoui,“FPGA implementationofI2C &SPIprotocols:A Comparative Study”, 16th IEEE International Conference on Electronics, Circuits and Systems (ICECS 2009), IEEE. 2009,pp.507 510.

[11] Martin Delvai, Ulrike Eisenmann, and Wilfried Elmenreich. “Intelligent UART module for real time applications”. Proceedings of the First Workshop on Intelligent Solutions in Embedded Systems,27 June 2009, pp.177 185.

[12] Junwei Zhou and Andrew Mason. “Communication buses and protocols for sensor networks”. Sensors 2.7 (2002),doi:10.3390/s20700244,pp.244 257.