International Research Journal of Engineering and Technology (IRJET) e ISSN: 2395 0056

Volume: 09 Issue: 06 | June 2022 www.irjet.net p ISSN: 2395 0072

International Research Journal of Engineering and Technology (IRJET) e ISSN: 2395 0056

Volume: 09 Issue: 06 | June 2022 www.irjet.net p ISSN: 2395 0072

Preethi T S1, Jayanth K Holalkeri2 , Manasa Dev G J3 , Manoj M Biradar4 , Nagesh R Shanbhag5

1Assistant Professor, Dept. of Electronics and Communication Engineering, Sapthagiri College of Engineering, Karnataka, India

2345 Student, Dept. of Electronics and Communication Engineering, Sapthagiri College of Engineering, Karnataka, India ***

Abstract Network on chip is a new prototype model in complex system on chips that provide an effective on chip communication networks. The information is transmitted through the interconnected modules in terms of packets. The main task of router is routing the data. So, the router architecture must be efficient with lower latency and higher throughput. In this project, we design and implement a 2D Network on Chip router mesh having four ports connected to other ports in four directions, namely North,South,West,East, and the fifth connected to the Local processing element through a network interface. This project is aimed to improve “Quality of Service” by employing algorithms like wormhole, routing, arbiter and crossbar switching.

Key Words: Bandwidth reservation, Flitting, Label switching, Networks on chip, Quality of Service, Streaming applications, System on Chip.

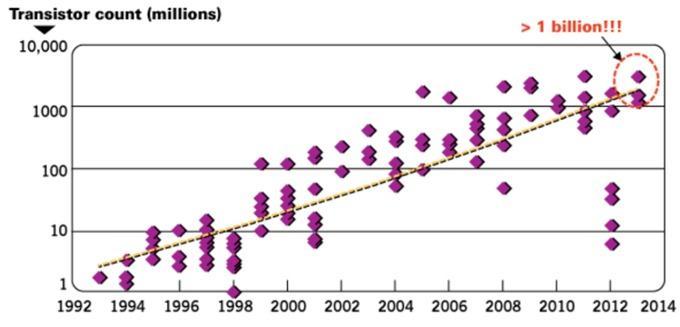

The recent technological advancements in the domain of semiconductorintegrationtechnologyistofillthenumberof workingtransistorsonanavailablechipareaforfabrication, satisfyingtheMoore’slawasshowninFig 1,whichresulted indevelopmentsoftechniquesandtechnologiesinthefield ofSystemonChip,hencethishasresultedwithnewarenato the work space of miniaturization and this has highly influenced by gate level circuit association for the Application Specific Integrated Circuit (ASIC). Then technologieshavetobedevelopedin linewiththedemands of market space and design time for execution, all these criteriaofinnovationstomeettheneedsofcommunication intheexistingdomainwhichleadthescopefortheevolving of networking on the same silicon chip for communicates leadingtotheeraofNetworkonChip

Network on chip is one such innovation known for its adaptation and flexibility of operation over the chip by satisfyingthefactorofpower,areaandnumberofgates.The ASICandSoCdesignapproachesarewellsuitedforvarious integrationofperipheralswithitsapproachesmeetingthe architecturalrequirementfortheminimizationofthedelay and effective communication among the devices in both simplexandduplexcommunicationcriteria.Thisleadstothe simplificationofvariousredundantinterconnectionsamong variousperipheralsintheconnectionplatformwhichshould befaulttolerantaswellforsuccessiveimplementationofthe desiredsystem.Butinthepresentscenario,fortheeffective on chipcommunicationdesign,SoCisthebestsuitedoption butnotfairenoughfortheeffectivecommunicationamong the peripherals. Hence, it requires reframing of the architecture to achieve minimum delay with maximum reliability, which can be obtained by interfacing NoC with SoC.

NoCbasedsystemsalsoplayavitalrolefordataexchange.To meettheneedsandrequirementsofdatahandlingoverthe different types of topology and algorithms for memory or buffer baseddatatransmissiononanFPGAdevice,itrequires DynamicallyReconfigurableNoC(DRNOC).Inthisprojectwe are bound to design a router under two dimensional structure.LaterthedesignisproposedingeneralizingtoNx N structure for the improvement of the properties of the FPGAviz,delay,throughput,LUTandflip flopsusingXilinx ISE platform for simulation and testing of the properties comparativelyovertheexistingsystems.

The paper [1] proposes switch model design and implementationforstudents’laboratoryactivities.Thethree staged switching architecture comprising of software and hardwaresystemswhicharebasedonmodular3x3switches, with controller as an Arduino microcontroller. The switch usesafewstagesofsmallerNxNcrossbarswitchestohelpin producing non blocking connections and forming an NxN network.Asthetiniestcomponentwithinwhichaswitching systemexists,isasquaredcross barswitch.Thisswitchhas tobedesignedinsuchawaythatitshouldbeabletoconnect all inputs to all its outputs. The blocking is due to busy destinationastheexperimentconductedalsoitshowcases 94%successfulconnectionswhile6%blockingisnotcaused duetobusyswitches,butduetobusydestinations.

International Research Journal of Engineering and Technology (IRJET) e ISSN: 2395 0056

Volume: 09 Issue: 06 | June 2022 www.irjet.net p ISSN: 2395 0072

The paper [6] examines the impact of failures on the reliability of the chips and develops corelating passive counterprotocolseithertopreventorrecoverfromthem.In thisview,severalschemeswereadaptedinordertoreduce variouskindsoferrorsymptoms,whileareaandpowerareat aminimum.Overanormaltransmissionscheme,itrequiresa 3 flittingre transmissionbufferpervirtual,sinceaflitmust bekeptfor3cyclesafteritleavesthecurrentnode.Theleast complextypeoftransmissionbufferisaQueueworkingon the principle of First In First Out (FIFO) buffer [25]. Such implementationtypehasoneinputportandoneoutputport, and has a control logic. The concept of deadlock has been enormously stressed upon. Some of errors mainly encountered in the router are VC allocator error, crossbar error,handshakingerror.Theschemeturnedouttobehighly effectivebothintermsoflatencyandpowerevenunderhigh errorrates.Allofthesemechanismsdescribedinthework helps in keeping the critical path of the Network on Chip routerintact.

The work proposed in [9] describes the design of on chip routersbasedonpowerconsumedanditsareaoccupiedby chip.Proposedarchitectureofon chiprouterinthisgivesthe resultsinwhichpowerconsumptionisreducedandsilicon area is also minimized. This router for NoC increases throughput, and introduces architecture which shows an improvementinFigureofMerit.Butincreasestheareaand powerduetoextracrossbarandarbiterscheme,andgotup to94%ofthroughput,whilepowerconsumptionisincreased by the factor of 1.28. [10] This approach reduces power consumption.Italsopointsatthebufferutilizationbymaking thechannelsbidirectionalandshowsdrasticimprovementin the performance of system. A router architecture with ReliabilityAwareVirtualRouterallocatesmorememoryto thebusychannelsandlesstotheidlechannels.Thissolution isdelayefficientbutnotareaandpowerefficient.

The paper [20] presents how a NoC topology, routing algorithmandswitchingarevitalincommunication. Inany NoC architecture, routing algorithm is an important key factor. The path chosen by the packet from source to destinationisdefinedbyaroutingalgorithm.XYalgorithmis one of the simplest routing algorithms used in NOC. The paper reviews a different XY routing algorithm that is implemented.Theuseofthisalgorithmistotallydependent ontheapplicationandenvironment.Theselectionofwhich totallydependsontheapplicationandthetrafficofpacketsin the network. Because the simplicity in implementation is importantinallarchitecture,XYroutingalgorithmiswidely used. The Dynamic XY routing algorithm achieves better balanceinloaddistributionandalsoprovidesdeadlock free and livelock free facility where the user can’t compromise withaccuracyofdatareceived,theygoforthefault tolerant routinglikeXYX.Finally,wecanconcludethatthechoiceof XY routing algorithm is totally dependent upon environmentalconditionofNOCarchitecture.

The paper [14] proposed an approach to find the shortest path distance between two nodes implementing on FPGA technology.TheFPGAarticulatesparallelismtosignificantly reducestepsascomparedtosequentialeffort.Inthispaper, A* algorithm is chosen for the shortest path distance calculationbasedonitsheuristicbehaviorsinceitachieves superiortimerunning.Shortestpathalgorithmsareapplied for applications like transportation and networking. If the shortestpathiscalculatedongeneralpurposeprocessor,to read the input there are separate instructions, and then computetheresulttoproducetheoutputwhichslowsdown theoverallperformance.Theresearchworkreducesdelayin findingtheshortestpath.Thisresearch[14]contributesin finding the shortest path with reduced delay by taking advantage of parallel processing in FPGA. A new design in coprocessorimplementationisproposedusingA*algorithms technique,andusingthisbringsintheconceptofparallelism.

Based on the literature survey and various studies, in this paperweareboundtodesignaLabelSwitchingNetworkon Chiproutercomprisingoffollowing:

1. Crossbarswitchtoestablishaconnectionfromeach inputtoeachoutput.

2. Arbitermoduletocheckportvalidityandtoflit.

3. ANoCmanagerusedforbandwidthallocation.

4. ALSrouterthatchecksiftherouterisvalidornot.

Wedesignandimplementallthemodulesmentionedabove, usingXilinxISE14.7andinstantiateitinatopmoduletoform asinglerouter.Furtherweimplementpoweroptimization techniquestoreducethepowerandimproveQoS.

The following steps are carried out to form an 8x8 NoC Router.

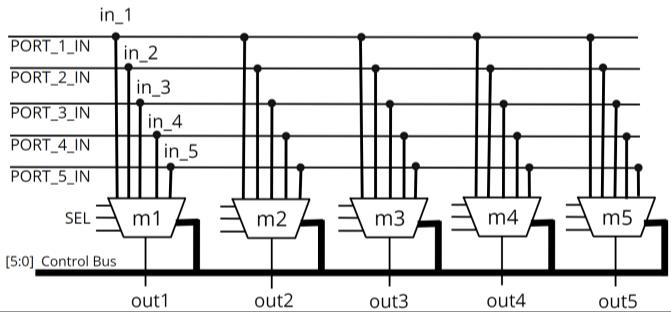

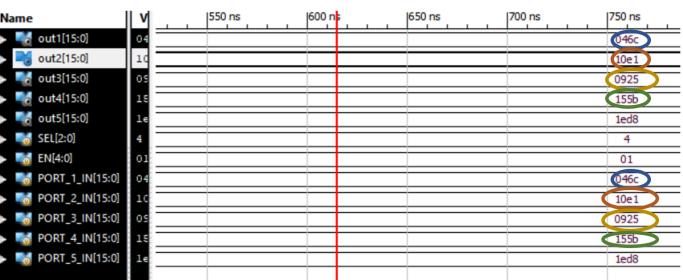

ACrossbarswitchisdesignedinXilinxISEasshowninFig 2.

1. Everyonchiprouterhas5portsnamely,Local,East, West,NorthandSouth.

2. Everyportneedstohaveonemultiplexer,therefore forfiveportsweneedfiveMUX.

3. Thecrossbarmodulehasseveninputportsandfive output ports and five wires for intermediate connections.

International Research Journal of Engineering and Technology (IRJET)

Volume: 09 Issue: 06 | June 2022 www.irjet.net

4. The5bitenablebusisusedtoenabletheparticular MUXand3bitselectlineisusedtoconnectinputtoa particularoutput.

5. Everypossibleconditionofenableandselectlines are specified and based on that condition the incomingportsandoutputportsareconnected.

6. The select line bits are determined by the arbiter modulediscussedbelow.

e ISSN: 2395 0056

p ISSN: 2395 0072

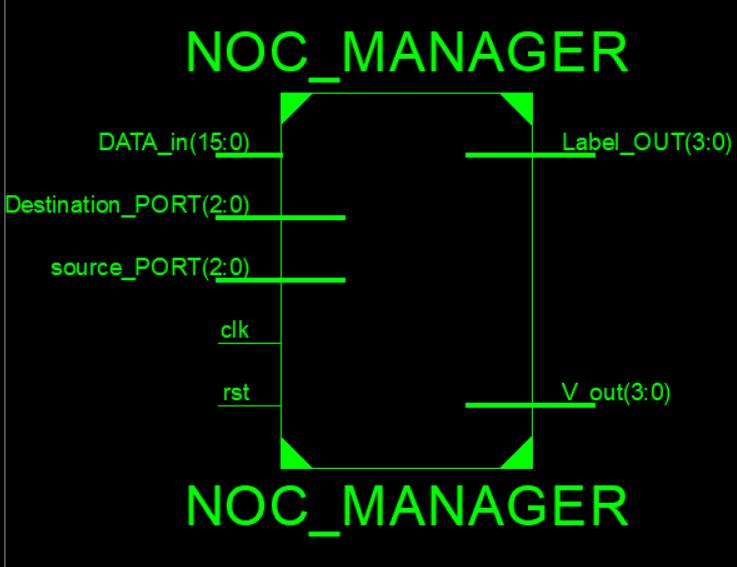

AnNoCmanagerisdesignedandtheRTLschematicisshown inFig 4.

1. NoCmanagerisusedtomonitortheusedandthe unusedbandwidth.

2. Itmainlyworksontheprincipleofedgedetection.

3. Edgedetectionbetweentwocorrespondingrouters isdonebyconsideringLSBbitsasshowninFig 5

4. EveryporthasoneNoCmanager,soforfiveports there are five NoC manager present in a single router.

5. Scaling factor is set to 5 between two slots and 2 betweenthepacketsinoneslot.

6. Onlyifthebandwidthisgreaterthan2,theportis consideredtobeavailable.

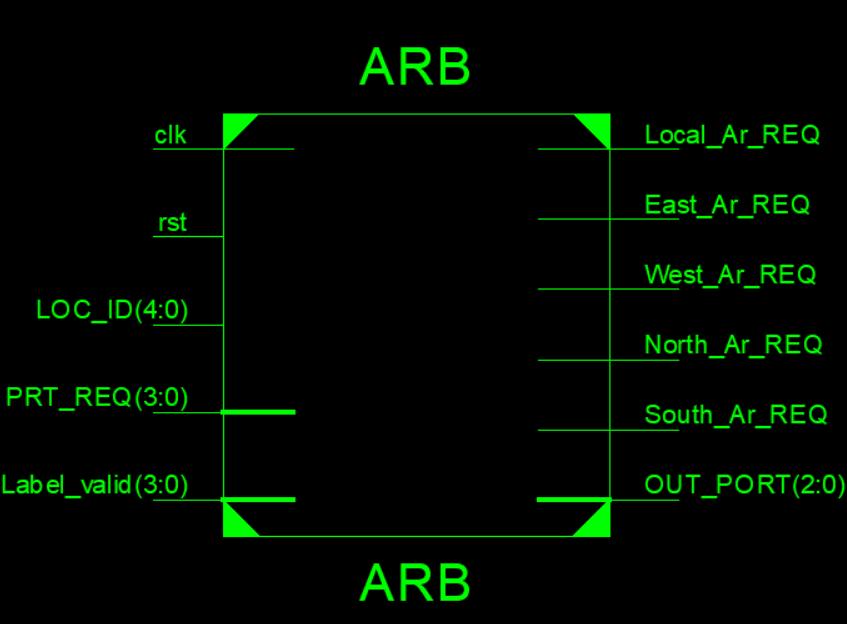

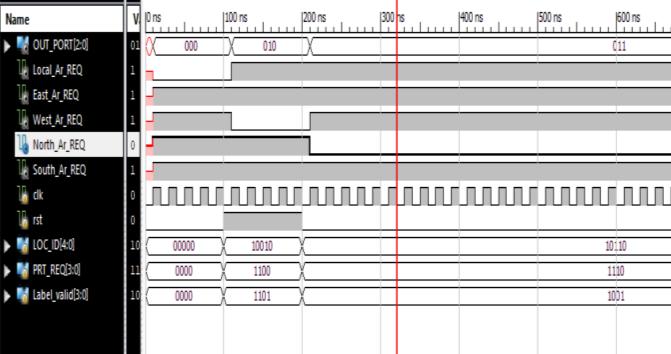

An arbiter module is designed in Xilinx ISE and the RTL schematicisshowninFig 3

1. An arbiter module is designed using arbiter algorithm and it consists of 5 input ports and 6 outputports.

2. Thismodulehelpstoflitthemessagebits.

3. Based on the condition of the destination ID and label,itchecksthevalidityoftheport.

4. Inferringtheselectconditionsofallthefiveports, theoutputportisallocatedwiththeselectlinebits usedincrossbarmodule.

Fig 4:RTLSchematicofNoCmanager

Fig -5:EdgeDetectionoccurringinNoCmanager

International Research Journal of Engineering and Technology (IRJET)

e ISSN: 2395 0056

Volume: 09 Issue: 06 | June 2022 www.irjet.net p ISSN: 2395 0072

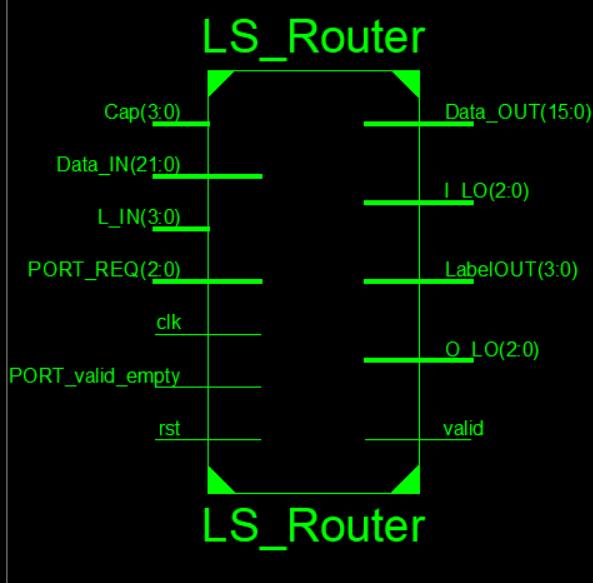

LabelswitchedrouterisdesignedandtheRTLschematic isshowninFig 6.

1. A label based switching router is connected to all thefiveports.

2. It also consists of a Queue module which implementsFIFOoperation.

3. Itisusedtogeneratelabelsandtocheckwhether portisvalidornot.

4. It checks whether received packet is valid or not andwhetherthepacketissuccessfullytransmitted ornot.

5. Italsocheckscongestionoftheport,iftheportisin use the packet is buffered in FIFO module and whethertheFIFOisfullornot.

Fig 7:SimulationresultsofCrossbarmodule

Fig 6:RTLSchematicofLSRouter

Crossbar Switch and Arbiter module are simulated and verifieditsoperationsuccessfully.Thesimulationresultsof crossbarandarbitermoduleareshowninFig 7andFig 8 respectively.

Fig 8:SimulationresultsofArbitermodule ThespecificationsforthisprojectismentionedinTable 1. Table -1: Design Specification

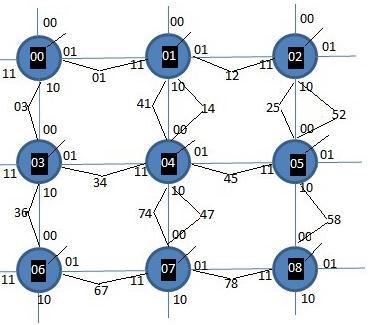

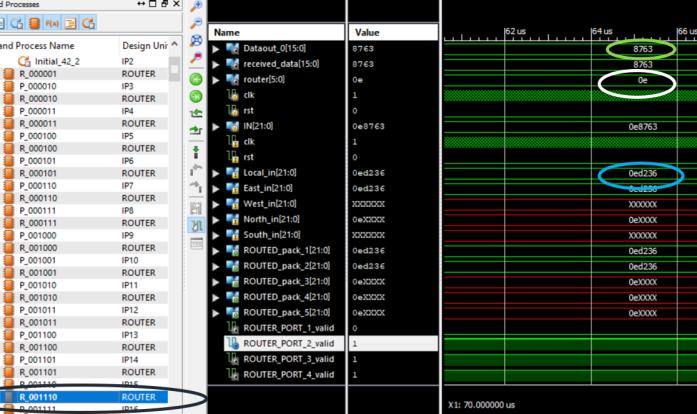

Once all the sub blocks are designed and verified, we instantiateallthemodulesinthetopmoduletoformasingle router.Apacketformatof22bitsisconsideredofwhich6 bitsdenotethesourceanddestinationaddress,remaining16 bitsdenotesthemessage.Thenthesinglerouterismultiplied 9 times to form a 3x3 router, and 64 times to form a 8x8 router.Toverifythefunctionalityof 8x8router,initiallya testbenchiswrittenandsimulated.Thesimulationresultsof the8x8routerareshowninFig 9.

Fig 9:Simulationresultsof8x8router

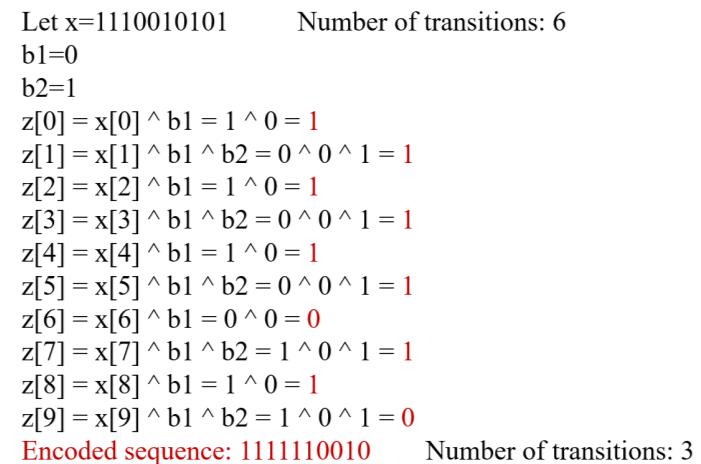

Before implementing it on the FPGA, we have written an algorithmtooptimizethepower.Thealgorithmisaimedto reduce the transitions in the message bits. For this we adopted the encoding and decoding techniques. Before transmittingthemessageisencodedusingthebitsb1and b2.Anycombinationofb1andb2canbetaken, butinthis project,wehavetakenb1as0andb2as1.Alltheevenbits areXORwithb1andoddbitsareXORwithb1andb2.The samedecodingtechniqueisusedatthereceivertoretrieve theoriginalmessage.AnexampleisshowninFig 10.From the figure we can see that the number of transitions is reducedfrom6to3,whichreducesthepowerconsumption duringtheprocessoftransmitting

Table

Logic Utilization Used Available Utilization

No.ofSliceregisters 21,325 126,576 16% No.ofSliceLUTs 28,005 63,288 44% No.ofoccupiedSlices 9,974 15,822 63% No.ofIOBs 40 296 13%

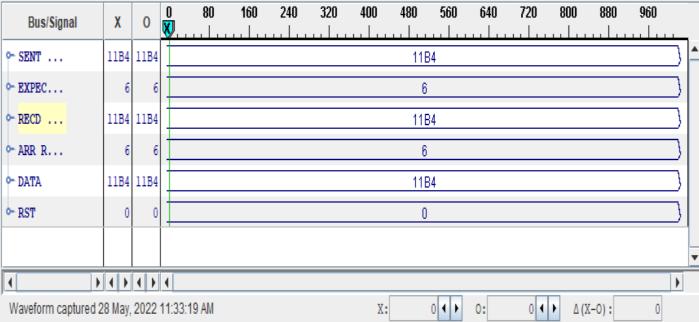

ChipScope Tool is used to implement the project and additionalfilesrequiredtoimplementarewrittenandadded asasourcetothetopmodule.Dataportwidthistakenas57 and classified 16 ports for sending data, 16 ports for receivingdata,16bitsforthedata,4bitsforexpectedand arrivedportand1portforreset.Thentriggersetupisdone andwaveformisaddedtothewindow.Theimplementation anditsresultsareshowninFig 1.

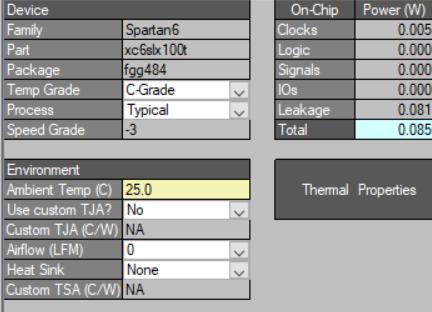

Aftersuccessfulverificationof8x8router,itisimplemented onFPGASpartan6.Thepowerconsumptionisobservedto be0.085WasshowninFig 11.Theareadetailsinthedesign summaryareshowninTable 2.

ThevariouschallengesinSoCdesignmadetheresearchers lookforbetteralternativesthatmadeawayforNetworkon chiptechnology.TheNoCiscurrentlystillinitsinitialstages andemergingresearcharea.NoChasaremarkableimpacton the SoC design of next generation and multicore architectures. For this project, various surveys and recent

International Research Journal of Engineering and Technology (IRJET) e ISSN: 2395 0056

research aspects of NoC, routing algorithms and network topology details were explored. An attempt was made to contributeintheresearchofNoCbyexploringthespaceof NoCrouterdesignwhichisapredominantcomponentofthe network. The main focus of this project is to design an efficient router since it is one of the most important components that determines various network parameters like latency, throughput and delay. The designing and simulationhavebeendoneusingthehardwaredescription languageVerilogHDLinXilinxISEtoolandimplementedon FieldProgrammableGateArray,usingChipScopeTool.

[1] Sani. A. and Fauzi. R, “Crossbar switch module implementationforlaboratorypurpose”,In Journal of Physics:ConferenceSeries,Vol.1235,No.1,p.012042, IOPPublishing,June2019.

[2] Islam, M.A., Arafath, M.Y. and Hasan, M.J., “Design of DDR4 SDRAM controller”, In 8th International Conference on Electrical and Computer Engineering, IEEE,pp148 151,December2014.

[3] Nikologiannis, A., Papaefstathiou, I., Kornaros, G. and Kachris,C.,“AnFPGA basedqueuemanagementsystem for high speed networking devices”, Microprocessors andMicrosystems,28(5 6),pp.223 236,2004.

[4] Agarwal, A., Iskander, C. and Shankar, R., “Survey of network onchip(noc)architectures& contributions”, Journal of engineering, Computing and Architecture, 3(1),pp.21 27,2009.

[5] Hecht,R.,Kubisch,S.,Herrholtz,A.andTimmermann,D, “Dynamic Reconfiguration with hardwired Networks on ChiponfutureFPGA”,InInternationalConferenceon FieldProgrammableLogicandApplications,2005,IEEE, pp527 530,August2005.

[6] Park, D., Nicopoulos, C., Kim, J., Vijaykrishnan, N. and Das, C.R., “Exploring faulttolerant network on chip architectures”, In International Conference on DependableSystemsandNetworks(DSN'06),IEEE,pp 93 104,June2006.

[7] Tsai,W.C.,Lan,Y.C.,Hu,Y.H.andChen,S.J.,“Networkson chips:structureanddesignmethodologies”,Journalof ElectricalandComputerEngineering,2012.

[8] Corbetta,S.,Rana,V.,Santambrogio,M.D.andSciuto,D., “A light weight Network onChip architecture for dynamically reconfigurable systems”, In 2008 International Conference on Embedded Computer Systems:Architectures,Modeling,andSimulation,IEEE, pp49 56,July2008.

[9] Kim, J., Park, D., Nicopoulos, C., Vijaykrishnan, N. and Das, C.R., “Design and analysis of an NoC architecture

fromperformance,reliabilityandenergyperspective”, In 2005 Symposium on Architectures for Networking and Communications Systems (ANCS), IEEE, pp. 173 182,October2005.

[10] Valinataj,M.,Mohammadi,S.andSafari,S.,“Fault aware andreconfigurableroutingalgorithmsforNetworks on Chip”, IETE Journal of Research, 57(3), pp 215 223, 2011.

[11] Shilpa. K. Gowda, “On Chip Network Design with Dynamic Reconfiguration”, International Journal of Scientific&EngineeringResearch,VolumeVI,IssueVII, pp1326 1329,July2015.

[12] Paramasivam, K., "Network On Chip and Its Research Challenges",ICTACTJournalonMicroelectronics(1.02), 2015.

[13] SeemaSreekumar,"NetworkonChipconfigurationand associated Algorithms", Journal of Emerging TechnologiesandInnovativeResearch(JETIR),Volume VIII,IssueIII.(ISSN 2349 5162),March2021.

[14] Idris,M.Y.I.,Bakar,S.A.,Tamil,E.M.,Razak,Z.andNoor, N.M, “High speed shortest path co processor design”, IEEE In 2009 Third Asia International Conference on Modelling&Simulation,pp626 631,May2009.

[15] Sao, P., Agrawal, R., “A Survey of Router Design Algorithms for NoC Platform and their Performance Analysis”,InternationalJournalofLatestTechnologyin Engineering,Management&AppliedScience(IJLTEMS), VolumeII,IssueVIII,pp73 76,2013.

[16] Cesário,W.O.,Lyonnard,D.,Nicolescu,G.,Paviot,Y.,Yoo, S., Jerraya, A.A., Gauthier, L. and Diaz Nava, M., “Multiprocessor SoC platforms: a component based design approach”, IEEE Design & Test of Computers, 19(6),pp52 63,2002.

[17] Sgroi, M., Sheets, M., Mihal, A., Keutzer, K., Malik, S., Rabaey, J. and SangiovanniVincentelli, A., “Addressing the system on a chip interconnect woes through communication based design”, In Proceedings of the 38th Design Automation Conference (IEEE Cat. No. 01CH37232),pp667 672,June2001.

[18] Yoo, Sungjoo, Gabriela Nicolescu, Damien Lyonnard, Amer Baghdadi, and Ahmed A. Jerraya, "A generic wrapper architecture for multi processor SoC co simulation and design.", In Proceedings of the ninth international symposium on Hardware/software co design,pp195 200,2001.

[19] Bahn,J.H.,Lee,S.E.andBagherzadeh,N.,“Ondesignand analysis of a feasible network on chip (noc) architecture”, In Fourth International Conference on InformationTechnology(ITNG'07),IEEE,pp1033 1038, April2007.

Volume: 09 Issue: 06 | June 2022 www.irjet.net p ISSN: 2395 0072 © 2022, IRJET | Impact Factor value: 7.529 | ISO 9001:2008 Certified Journal | Page461

International Research Journal of Engineering and Technology (IRJET) e ISSN: 2395 0056

Volume: 09 Issue: 06 | June 2022 www.irjet.net p ISSN: 2395 0072

[20] Chawade,S.D.,Gaikwad,M.A.andPatrikar,R.M.,“Review of XY routing algorithm for network on chip architecture”, International Journal of Computer Applications(IJCE),43(21),pp.975 8887,2012.

[21] Sayankar, B.B., Agrawal, P. and Dorle, S.S., “Routing AlgorithmsforNoCArchitecture:ARelativeAnalysis”,In 20136thInternationalConferenceonEmergingTrends in Engineering and Technology, IEEE, pp 105 106, December2013.

[22] Sani, A, "Multistage switching hardware and software implementations for student experiment purpose", In IOP Conference Series: Materials Science and Engineering,Vol.309,no.1,p.012097,2018.

[23] Talwar,B.andAmrutur,B,“TrafficengineeredNoCfor streaming applications”, Microprocessors and Microsystems,37(3),pp333 344,2013.

[24] Kendaganna, S.S., Jatti, A. and Uma, B.V., “Design and implementation of secured agent based NoC using shortestpathroutingalgorithm”,InternationalJournal of Electrical and Computer Engineering(IJECE), 9(2), p.950,2019.

[25] Yang, Z.J., Kumar, A. and Ha, Y., “An area efficient dynamicallyreconfigurablespatialdivisionmultiplexing network on chipwithstaticthroughputguarantee”,In 2010InternationalConferenceonField Programmable Technology,IEEE,pp.389 392,December2010.

PreethiTS, AssistantProfessor,Dept.ofECE SapthagiriCollegeofEngineering Email: ts.preethi@gmail.com

JayanthKHolalkeri, Student,Dept.ofECE SapthagiriCollegeofEngineering Email: jayanth.holalkeri@gmail.com

ManasaDevGJ, Student,Dept.ofECE SapthagiriCollegeofEngineering Email: manasadev30@gmail.com

ManojMahadevBiradar, Student,Dept.ofECE SapthagiriCollegeofEngineering Email: mmbiradar1906@gmail.com

NageshRShanbhag, Student,Dept.ofECE SapthagiriCollegeofEngineering Email: nageshrshanbhag619@gmail.com