Volume: 09 Issue: 06 | June 2022 www.irjet.net p ISSN:2395 0072

Volume: 09 Issue: 06 | June 2022 www.irjet.net p ISSN:2395 0072

Rose Mathew1, Anchana Babu2, Milna M S3, Er. Ashly John4

1 3Students, Dept. of Electrical Engineering, Saintgits College of Engineering, Kerala, India 4Asst. professor, Saintgits College of Engineering, Kerala, India ***

Abstract -In the area of VLSI design, summing circuits are one of the most widely used entities in processor data path architecture. Therefore, the performance of a processor is greatly influenced by the action of the resident adders. With the advances in VLSI technology, research works are emerging on designing architecture with low power consumption, high speed, less area, or a combination of them. The thing is no existing adders can fulfill all these 3 criteria. Here we are implementing a modified carry select adder with Brent Kung adder using the modified gate diffusion input technique. A carry select adder consists of multiple pairs of Ripple carry adders which give it the most complex design and longer computation time and thus the performance of the CSA will dropdown. Hence, we replaced RCA with BKA which is a parallel prefix adder that has the best performance till now. So,with this replacement, the performance of the CSA gets improved but the area consumption and the power consumption will be increased. For that, we are using the MGDI technology. MGDI is the latest technique that reduces the number of transistors and thereby the area and power consumption. Therefore, all three criteria are satisfied in this modified CSA adder.

Key Words:CSA, BKA, MGDI, Parallel prefix adder, Area, Power, Delay

Adders are the fundamental building blocks of digital circuitdesign.Addersaretheelementaryblocksinvarious dataprocessors,soiftheadderisaninefficientonethenit will affect the overall performance of the processor. Hence, the adder must be efficient and good in performance. The three major parameters that affect the performance of an adder are area, delay, and power. No existing adders satisfy all these 3 criteria. Conventional adderssuchasRCA,CLA,CSA,etc.arenotmuchefficientto meet the requirements of the new technology. Therefore, in current technology, the parallel prefix adders are the fastest adders with better performance. Even though chip areaandpowerconsumptionareless,high speedaddition of large numbers is possible. Primitive carry select adder consists of multiple pairs of RCAs which gives it a more complex design and longer computation time, this makes the CSA low in performance. Here we replace these RCAs with BKAs which is a parallel prefix adder. To make the adderarea efficientweintroduceMGDItechnology,which effectivelyreducesthenumberoftransistors.

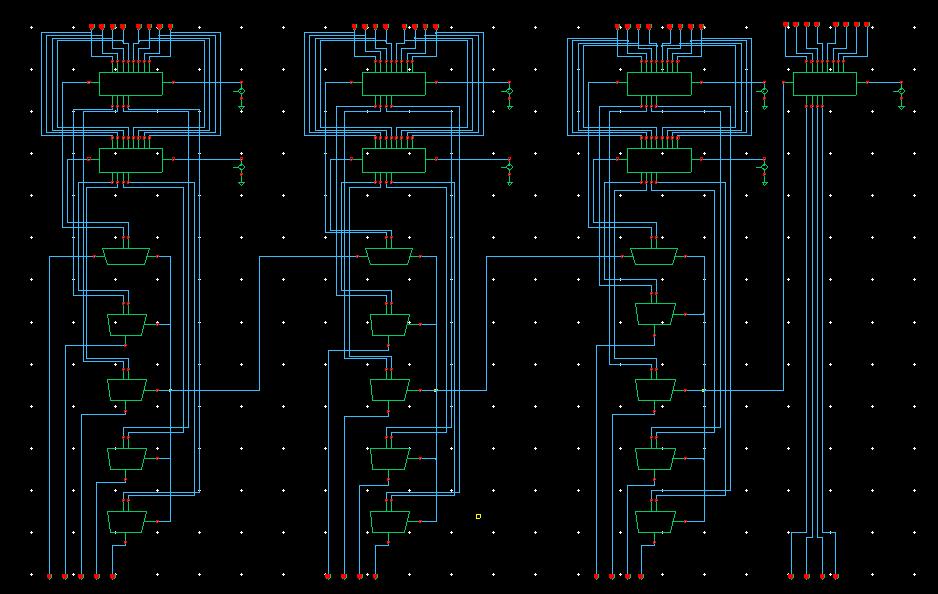

Parallel prefix adders are one of the most high performance adders with less design complexity. In a parallel prefix adder, the computation of carry occurs simultaneously. This parallel computation of carries makes it fastest in its performance. There are three main stages for the computation. They are the pre processing stage, carry generation stage, and post processing stage In preprocessing, the computation of generate and propagatesignalsofcorrespondingpairsofinputsoccurs. Theequationsofgenerateandpropagatesignalsaregiven below:

pi=ai⊕bi (1) gi=ai.bi (2)

Thecarrygenerationstageincludesthecomputationof carries corresponding to each pairs of input bits. The equationforcarrygenerationisasfollows:

pi:j=pi:k.pk 1:j (3) gi:j=gi:k+(pi:k.gk 1:j) (4)

The post processing stageincludesthecomputation of the final sum bits. The equation for the post processing stageisasfollows: si=pi⊕ci 1 (5)

Thepre processing stage is the first stage in the parallel prefix adder. It includes the computation of pi and gi signalsasshowninequations(1)and(2).

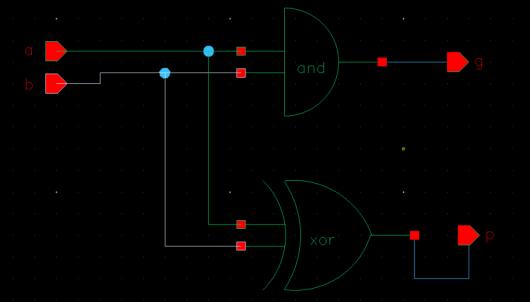

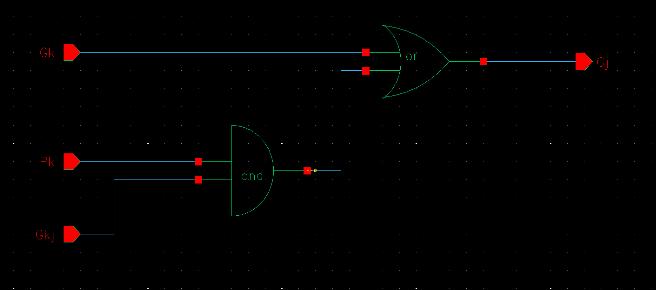

Fig 1:Pre processingstage

International Research Journal of Engineering and Technology (IRJET) e ISSN:2395 0056

Volume: 09 Issue: 06 | June 2022 www.irjet.net p ISSN:2395 0072

In this stage, carry computation occurs. The carry signal generated from one stage will proceed to the next stage and this process continues for all other stages. The equation for the computation is shown in equations (3) and(4).

Black cell: Black cell performs the computation of both propagateandgeneratesignals.Itisacombinationofboth greycellsandANDgate.

These three cells combine to form the carry generation stage. The diagram of the carry generation block is as follows:

Fig-2:Blackcell

Grey cell: Grey cell computes the generate signals which are used in the computation of sum bits in the post processingstage.ItisacombinationofANDandORgates.

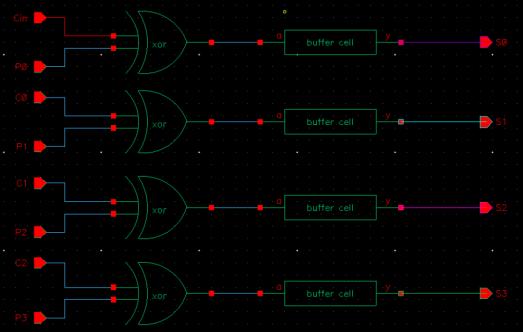

This is the final stage in the parallel prefix adder computation.Inthisstage,thefinalsumbitsareobtained. The procedure to obtain the final sum bits are shown in equation(5).

Fig 3:Greycell

Buffer cell: A buffer cell is used to balance the loading effect. It is a combination of NOT gates in series. It also strengthenselectronicsignals.

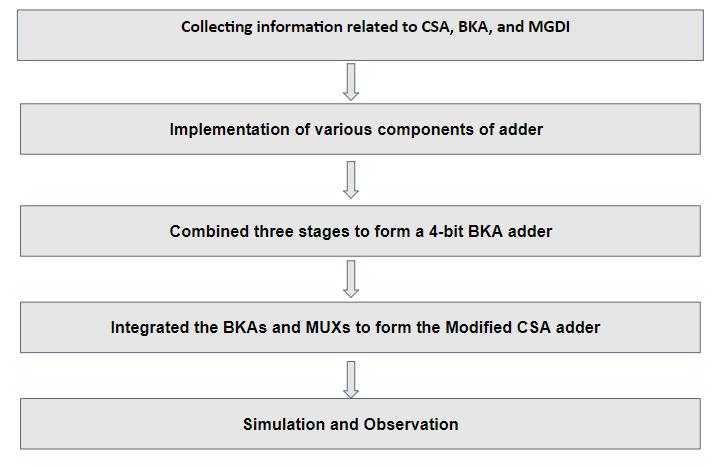

Asimulationstudyofa 16 bitmodifiedcarryselectadder using the cadence virtuoso tool is developed by following thestepsshownbelow:

Fig 4:Buffercell

Fig 7:Flowgraph

International Research Journal of Engineering and Technology (IRJET)

Volume: 09 Issue: 06 | June 2022 www.irjet.net

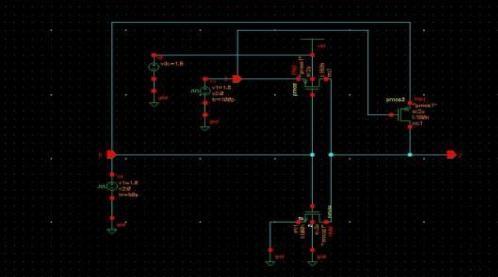

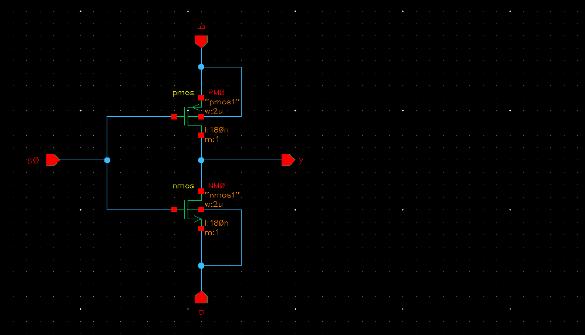

The basic logic gates are the fundamental building blocks of any digital circuit. There are seven basic logic gates among all of them we use the three logic gates such as AND, OR, and XOR. All these gates are implemented using the MGDI technique which in turn reduces the number of transistorsineachgate Hence,theareaconsumedbyeach gatewillbelessthantheCMOSlogic.

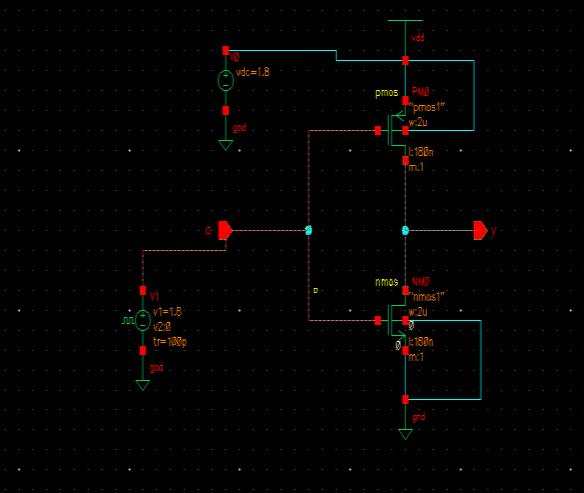

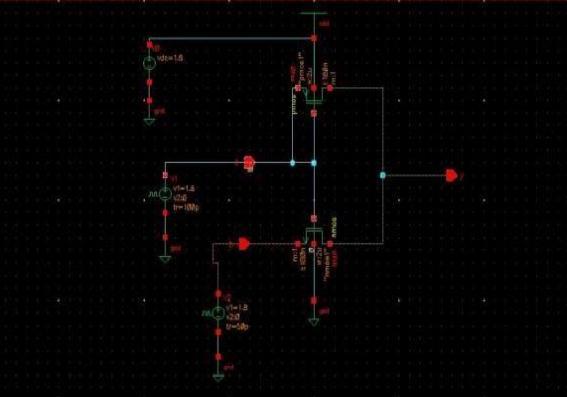

AND gate: The AND gate which is implemented by CMOS technologywillbehavingatleastasetof6transistorsbut the AND gate that we implement by MGDI technology needsonly2transistorswhichmeanswecansaveupto4 transistors in a single AND gate. We need plenty of AND gates in our design of an adder so this reduction is very significantaccordingtous.Thetransistor leveldiagramof ANDgateusingtheMGDItechniqueisshownbelow:

OR gate: The same is applicable for OR gate also, a CMOS logicORgatestructurerequires6transistorsbutanMGDI ORgateneeds2transistorsforitsworking

XOR gate: In the case of the XOR gate, we need only 3 transistors for its working by MGDI technique, the same xor should need a 6 transistor setup to work in a CMOS technique. so, in a xor gate also we saved up to 3 transistors.

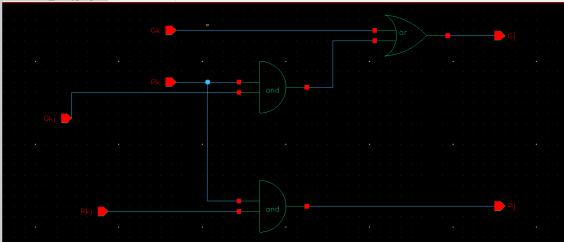

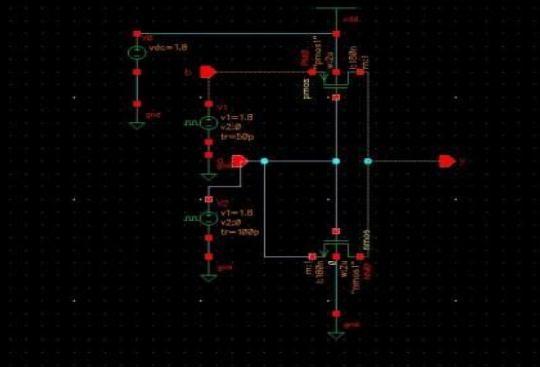

Fig 10:XORgate

Brent kung adder is a fastest adder among all the parallel prefixadders.Ithasaverysimpledesignarchitectureand wiring complexity is very less. It has three intermediate stagesfrominputtooutput,theyarepre processing,carry generation, and post processing. . Parallel prefix adders areauniqueclassofaddersthataremoreefficientintheir work than all other primitive adders and they are based on generating and propagating signals In our proposed BKA model we implemented each stages of BKA using MGDI technique. Thus the number of transistors required is very less compared to the CMOS technique. Hence the area consumption is reduced. In BKA the critical path is very less, since it is a parallel prefix adder thus the delay willbeveryless.

Fig 11:4 bitBKA

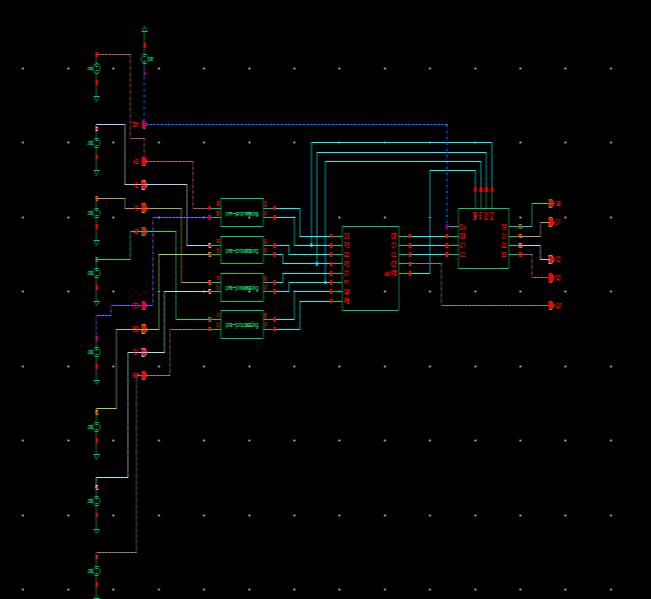

Multiplexers are structural blocks that select between multiple input signals. A multiplexer has multiple data inputs in1, 2, …N, a select line sel, and a single output signal out. The value of the select line determines which input signal should be shown on the output. The muxes usedhereinthisprojectare 2:1muxes.Thatmeansthere

International Research Journal of Engineering and Technology (IRJET) e ISSN:2395 0056

Volume: 09 Issue: 06 | June 2022 www.irjet.net p ISSN:2395 0072

will be two input signals to select between (in0 and in1) andtheselectlinewillbeasinglebit.Iftheselectlineis0, thentheoutputsignalisin0.Iftheselectlineis1,thenthe outputsignalwillbein1.Inthisproject,weusethemuxto selectthezerocarryoronecarrysumfromtheBKAs.Here weuseseveralpairsofmuxesforthiswork.Thisisavery significantstepintheadditioncalculationofourmodified CSA. Mux will select the desired output from one of the addersandwill outputit, whichisthefinal sumoutput of ourmodifiedCSA.

weusetheMGDItechnologyorthemodifiedgatediffusion input technology. This technology is all about the reductionofthenumberoftransistorsfromthegatelevel. By using just 2 transistors we can build each of the gates which helps us in a great area reduction. So, by such a reduction in the number of transistors, the power consumption will also be significantly reduced and thus wesatisfiedallthethreefactorsforanefficientadder.

Carry select adder is one of the oldest but still most relevant basic adder. Its non linear dependency for the calculation of the carry output makes it distinct and most used principle in modern adders. CSA will calculate the outputforcarryforallpossibleinputsie;logicinput1and 0. The calculation for possible input is done by using adders. Multiplexer is used to select between the generatedpossibleoutputs.HenceitisclearthatCSAdoes nothavetowaittogenerateoutput,thismakesthisadder oneofthefastestadder.

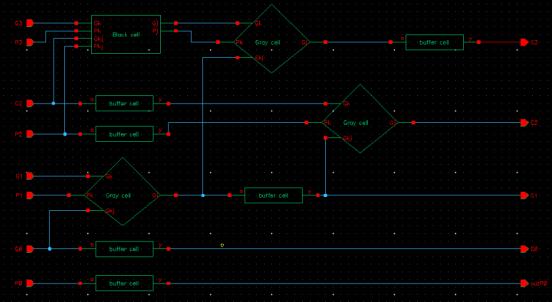

The modified carry select adder we implemented has differencesfromtheoriginalcarryselectadderin2areas, thatare,RCAsarereplacedwithBKAswhichareoneofthe most high performance adders existing. In carry select adder always 2 bit RCAs are used but here we efficiently used 4 bit BKAs. The second difference is in the usage of multiplexers,multiplexersareplacedinadifferentwayin the implementation. Carry Select Adder uses a pair of Ripple Carry Adders (RCA) for Cin=0 and for Cin=l but as we know the performance of RCAs is not that excellent and RCAs create a much large delay for higher bit calculations,sointhisproject,wereplacetheseRCAswith BKAswhichisoneofthemostefficientandfastestparallel prefix adders existing. But as we know by replacing RCAs with BKAs we can only satisfy the performance need of our new adder, our strategy is to form a new adder with excellent power, performance, and area consumption. So, we have to minimize the area consumption for that here

Fig5.1.ModifiedCarrySelectAdder

Conventional Carry Select Adder consists of ripple carry adder.BrentKungadderhasreduceddelayascompareto ripple carry adder. We use tree structure from in Brent Kungaddertoincreasesthespeedofarithmeticoperation.

The project performs in EDA Tool, Cadence Virtuoso. One ofthethreeparameters,Areaisalsocalculatedinthistool. The graphical representation of comparison of area in conventional CMOS logic and by using MGDI technique is showninfig.6.1

AREA

0 500 1000 1500 CMOSMGDI

Fig6.1:ComparisonofareabetweenCMOSandMGDI techniqueinCadenceVirtuosotool

International Research Journal of Engineering and Technology (IRJET) e ISSN:2395 0056

Volume: 09 Issue: 06 | June 2022 www.irjet.net p ISSN:2395 0072

The result analysis shows that MGDI technique shows better results than the conventional CMOS logic in terms ofarea.

Power and delay is other design parameter. Power consumption and delay of this circuit is calculated in Cadence Virtuoso. . The graphical representation of comparison of power consumption and delay in conventional CSA and CSA with BKA is shown in fig 6.2. TheresultanalysisshowsthatCSAwithBKAshowsbetter results than the conventional CSA in terms of Power consumptionanddelay.

highspeed,andcanbeused invariousadderapplications such as multipliers, to execute different Digital Signal Processing algorithms such as Finite Impulse Response, InfiniteImpulseResponse,andsoon.

[1] Anas Zainal Abidin, Syed Abdul Mutalib Al Junid, Khairul KhaiziMohd Sharif, Zulkifli Othman, Muhammad AdibHaron “4 bit Brent Kung Parallel Prefix Adder Simulation Study Using Silvaco EDA Tools”DOI10.5013/IJSSST

[2] Pappu P. Potdukhe, Vishal D. Jaiswal “Design of High Speed Carry Select Adder Using Brent Kung Adder” International Conference on Electrical, Electronics, andOptimizationTechniques(ICEEOT) 2016

[3] GTejaswini,VJagannaveen,JVsuman“Designoflow power ful adder using MGDI logic” European Journal of Molecular & Clinical Medicine, ISSN 2515 8260 Volume7,Issue4,2020

Fig6.2:ComparisonofpowerbetweenCSAandmodified CSAinCadenceVirtuosotool

[4] Mr. Deepak Raj, Mrs. Sahana K Adyanthaya , Prof. Praveen J, Prof. Raghavengra Rao R “Design and Implementation of different types of efficient paral el prefix adders” International Journal Of Innovative Research In Electrical, Electronics, Instrumentation And Control Engineering And National Conference on advanced innovation in engineering and technology (ncaiet 2015) alva’s institute of engineering and technology,moodbidrivol.3,specialissue1,april2015

[5] P.BNatarajan,SamitKumarGhoshandR.Karthik“An efficientcarry select adder ” International Conference on Electronics, Communication & Aerospace TechnologyICECA2017

Fig6.3:ComparisonofdelaybetweenCSAandmodified CSAinCadenceVirtuosotool

ICdesignhasalwayssoughtthebestpossibleperformance onICdevelopmentintermsofspeed,powerconsumption, and area. This study paper found that incorporating the MGDI technique in any design can reduce the area of the circuit to a most satisfying extent. This work may also be expanded to a larger number of bits. With the advent of parallel prefix adder, the latency and power consumption ofvariousadderdesignsarelowered.BrentKungadderis chosen because parallel prefix adders produce quick results. When compared to conventional CSA adder architectures, the calculated results show that BKA Carry SelectAdderisbetterintermsofpowerconsumptionand

[6] Er. Aradhana Raju, Richi Patnaik, Ritto Kurian Babu, PurabiMahato “Paral el Prefix Adders A Comparative Study For Fastest Response” 2016 International Conference on Communication and Electronics Systems,DOI:10.1109/CESYS.2016.

[7] Basavoju Harish, Dr.K.Sivani, Dr.M.S.S.Rukmini “Design and Performance Comparison among Various types of Adder Topologies” Third International Conference on Computing Methodologies and Communication(ICCMC2019)