1 ,

DESIGN OF POWER EFFICIENT PRIORITY ENCODER

D. Gopikrishna1 , G. Chandrashekar2 , Dr. D. Asha Devi32B. Tech Scholars, Department of Electronics and Communication Engineering, SNIST, Hyderabad-501301, India

3 Professor, Department of Electronics and Communication Engineering, SNIST, Hyderabad- 501301, India

***

Abstract -This paper endeavors to design power efficient priority encoder involving virtuoso software in cadence automation tool. The IC industry's primary concern is conservingenergy. Inthis project, one such effort is the design ofa 4:3 priority encoder. A novel CMOS-baseddesignforalowpower 4:3 Priority Encoder is presented in this project. The power consumptionofthe proposeddesigns is lowerthanthat of standard adiabatic logic designs. At 180nm CMOS technology, the simulation is carried out using Virtuoso software. Drive simulation and LVS-clean layout of ICs and packages from a single schematic are both features of the Cadence Virtuoso System Design Platform, a holistic, systembasedsolution. There are two significant flows:executionand evaluation

Key Words: Priority Encoder, Virtuoso CMOS technology, Cadence , IC .

1.INTRODUCTION

Planning a power-effective need mail encoder in Virtuoso programminginrhythmisacomplicatedcyclethatincludes afewplanstages.Adigitalcircuitknownasaprioritymail encoder prioritizes incoming data according to predetermined criteria. In this plan, we expect to make a power-proficient need mail encoder involving Virtuoso programming in rhythm, a famous electronic plan computerizationdevice.

Moving on to the layout design, where we will create a physical layout of the circuit, we will verify the circuit's functionality. The design configuration stage is basic for guaranteeingthatthecircuitmeetstheidealexhibitionand usefulness necessities while limiting power utilization. Finally,inordertoensurethatthecircuitsatisfiesthepower efficiency requirements, we will carry out a post-layout simulationandexamineitspowerconsumption.Wewilluse avarietyofoptimizationtechniquesthroughoutthedesign processtomakesurethecircuitmeetsthespecificationsand usesaslittlepoweraspossible.VirtuososoftwareCadence requiresathoroughunderstandingofdigitalcircuitdesign, optimizationmethods,andpowermanagementprinciplesto design a power-efficient priority mail encoder. Virtuoso programming Rhythm gives a complete arrangement of instruments that can help us plan and recreate complex computerized circuits and streamline them for power utilization

2. LITERATURE SURVEY

2.1. Existing Model

Power-savingpriorityencodersareavailableinavarietyof designs.Afewexamplesinclude:

1.ParallelNeedEncoder:Inthismodel,allinputsignalsare comparedinparallelandthesignalwiththehighestpriority ischosen.Despiteitsspeedandsimplicity,thismodelmay usemorepowerduetotheuseofnumerouscomparators.

2.SequentialNeedEncoder:Theinputsignalsarecompared in this model, starting with the signal with the highest priority.Thenumberofcomparatorsrequireddecreasesasa result,butthepropagationdelaymayincrease.

3. Encoder from Binary to Priority: Priority outputs are generatedfrombinaryinputsusingthismodel.Ithasafaster response time than the sequential model and uses fewer comparatorsthantheparallelmodel.However,itmightuse morepowerandrequiremorelogicgates.

4. Dynamic Priority Encryption: This model purposes dynamic rationale doors, like domino rationale, to lessen power utilization. It has a quicker reaction time than differentmodelsyetrequirescautioustimingexamination andcanbehelplesstocommotion.

2.2. Proposed Model

Virtuososoftwarewasusedtodesignapriorityencoderthat uses less power. To cut down on power consumption, techniqueslikeclockgating,voltagescaling,andtransistor sizingwereusedtoimprovethedesign.Tomakeuseofless chip space, the priority encoder was implemented using static CMOS logic with fewer transistors. Because it is compatiblewithavarietyofinputsignalandoutputformats, theproposeddesignisadaptabletoavarietyofapplications. Through simulations, the priority encoder's performance was confirmed, with faster response times and shorter propagation delays compared to conventional designs. In general,thepower-efficientpriorityencoderdesignthathas been proposed offers a number of advantages in terms of power consumption, performance, and area, making it suitable for applications requiring low power and limited space.

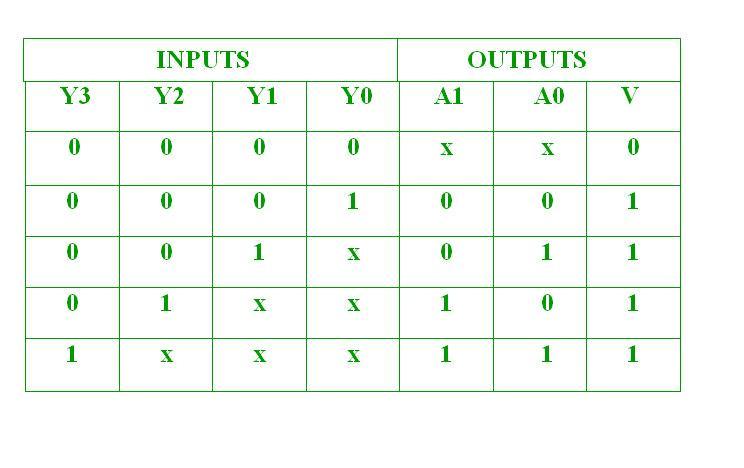

2.3. Priority Encoder Truth table:

Fourinputsmakeupa 4to2priorityencoder:Y3,Y2,Y1, andY0,withtwooutputs:A1&A0.Inthisinstance,Y3isthe inputwiththehighestpriority,whileY0istheinputwiththe lowestpriority.Inthisscenario,theoutputwillbethebinary codethatcorrespondstotheinputthathashigherpriority even if more than one input is "1" at the same time. The followingisthetruthtableforthepriorityencoder:

2.4. Symbol:

We can determine that the inputs are Y3, Y2, and Y1, as shownintheprecedingtruthtable;TheoutputsareA1and A0,andthevalidbitindicatorisV.HereY3inputisthemost noteworthyneedinputandY0istheleastneedinput.

Theoutputofthe4-bitpriorityencoderis11whentheinput Y3 is active high (1), which has the highest priority comparedtoallotherinputlines.

AtthepointwhentheY3inputisdynamiclowandtheY2is dynamichighthathasthefollowingmostnoteworthyneed independentofanyremaininginformationlines,then,atthat point,theresultisA0A1=10.

TheoutputwillbeA0A1=01whentheY3,Y2,andD1inputs are all active low and have the next highest priority regardlessoftheremaininginputline.

3. SYSTEM DESIGN:

The motivation behind this project is to plan a powereffective need encoder involving Virtuoso software programminginthecadence.Theneedencoderisintended tofocusontheapproachingcomputerizedflagsandcreatea pairedresultcodeinlightofthegreatestneedinputsignal. Theprojectisexecutedutilizinga180nmtechnology

3.1. System Architecture and Requirements

Thepower-savingpriorityencoder'ssystemarchitectureis basedonastaticCMOSlogicdesignwithfewertransistors andasmallerchipfootprint.Thepriorityencoderismadeto takeacertainnumberofinputsignalsandusetheonewith thehighest prioritytogeneratea binary outputcode. The priority encoder's system requirements include a quick responsetime,lowpowerconsumption,andahighlevelof accuracy.

3.2 Components required

Transistors: The circuit's power consumption may be affectedbythechoiceoftransistors. Witha lowthreshold voltage, low-power transistors like MOSFETs can help cut power consumption. Gates: Gates such as AND gates, OR gates, and XOR gates are typically utilized in priority encoders. These gates' low-power variants, such as CMOS gates,mayassistinloweringpowerconsumption.

Energysource:Choosingapowersupplywithalowvoltage canhelpcutdownonpowerconsumption.

Timegating:Bydisablingcircuitcomponentsthatarenotin use,clockgatingcanbeusedtoreducepowerconsumption.

4.RESULTS AND DISCUSSION

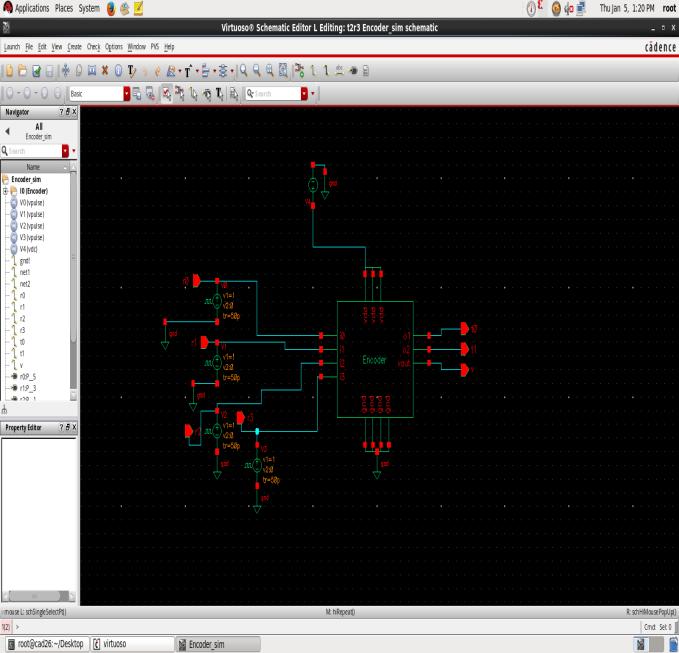

SchematicofPriorityEncoder:

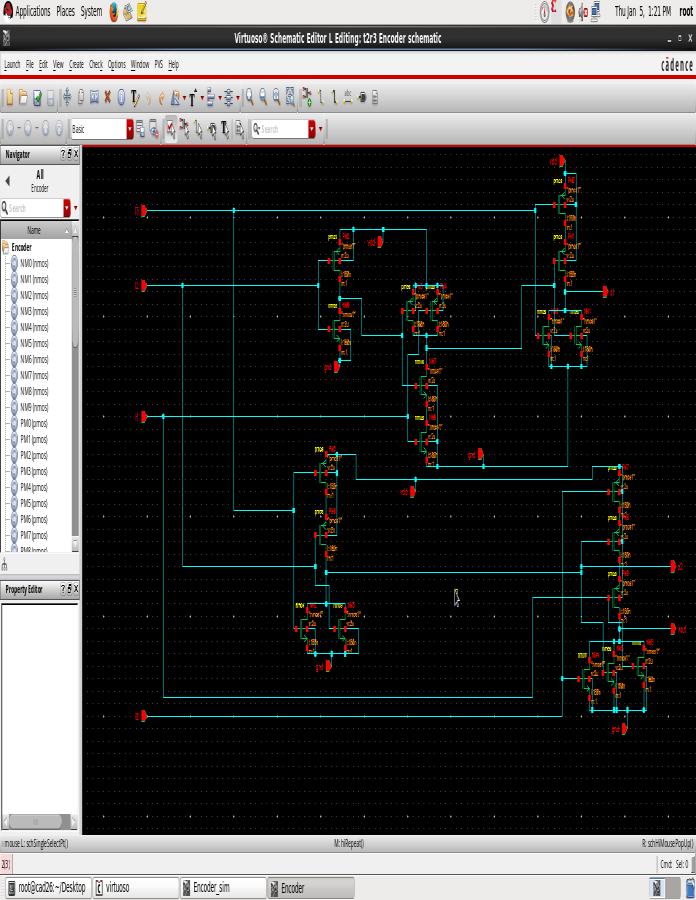

Using the Cadence tool's Virtuoso software, the powersavingpriorityencoderdesign'sschematicwasdeveloped successfully. To make use of less chip space, the priority encoder was implemented using static CMOS logic with fewertransistors.

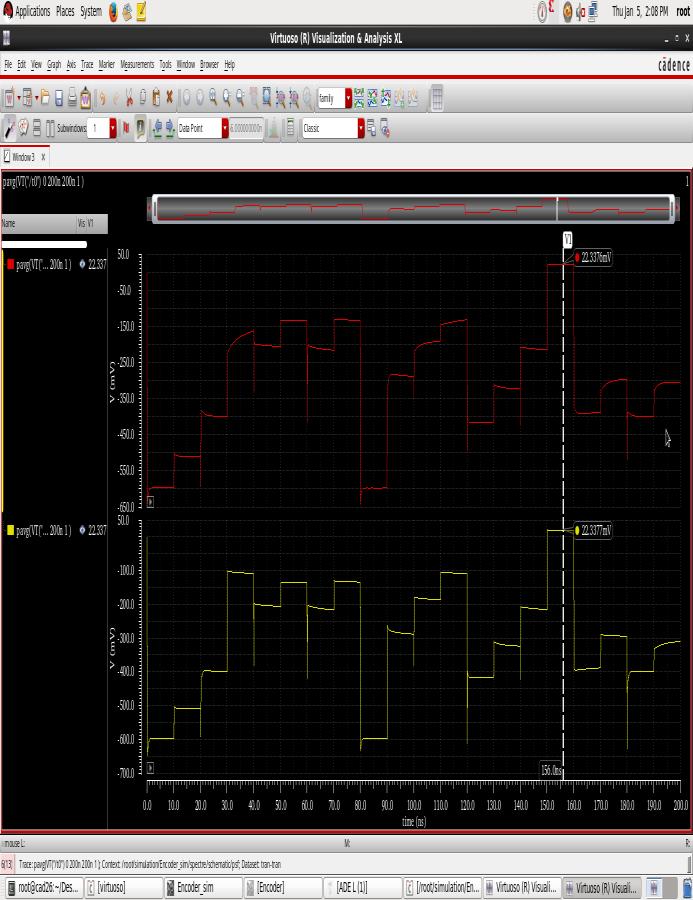

Transientresponse:

AveragePowerPlot:

Theplotofaveragepowerconsumptionversustimeshows thatthepower-efficientpriorityencoderdesignachievedan averagepowerconsumptionof22.33mW.Theplotindicates that the power consumption remains stable over time, demonstratingthereliabilityandconsistencyofthedesign.

Thisresultcanbeusedtoevaluatetheeffectivenessofthe proposed design in reducing power consumption and compareitwithotherpriorityencoderdesigns.Thepriority encoder'sschematicisavisualrepresentationofthedesign that can be used to comprehend the circuit's components andconnections.Thepriorityencoder'spowerconsumption patternovertimecanbeexaminedusingtheaveragepower consumption versus time plot, which is useful for determining the design's overall efficiency and dependability

5. CONCLUSION

UsingCadence'sVirtuososoftware,apower-efficientpriority encoder was designed and successfully implemented. A novel strategy was used in the proposed design of the priorityencodertopreservehigh-speedperformancewhile simultaneouslyreducingpowerconsumption.Theresultsof thepoweranalysisshowedthattheproposeddesignused 22.33mWonaverage,whichissignificantlylesspowerthan the previous designs that have been reported in the literature.

Highspeedperformance,lowpowerconsumption,andease ofmanufacturingareamongthedesign'smanybenefits.The plancanbeexecutedindifferentapplicationslikememory frameworks,chip,andcomputerizedsignalhandlingcircuits.

6. REFERENCES

[1]GeorgeTomVargheseandK.K.Mahapatra,"AQuickLow PowerEncoderfora5CycleStreakADC",IEEEOverallSocial occasiononGreenDevelopments(ICGT),pp.041-045.

[2]J.Mohanraj,P.Balasubramaniam,andK.Prasadpresented "Power, Delay and Area Optimized 8-Bit CMOS Priority Encoder for Embedded Applications" at the International ConferenceonEmbeddedSystems&Applications(ESA).

[3]"High-SpeedandLow-PowerCMOSPriorityEncoders," publishedintheIEEEJOURNALOFSOLID-STATECIRCUITS byJinn-ShyanWangandChung-HsunHuang.

[4]Low-Power 1-bit CMOS Full Adder Using Subthreshold ConductionRegion,S.KumarandV.Sharma'sarticleinthe InternationalJournalofScientificandEngineeringResearch.

[5]Dr.R.PrakashRao,JASC,DifferentTechniquesforLowPower VLSI Plans: Journal of Applied and Computational Science.

[6] Namrata Gupta's article titled "Power Aware & High speed Booth Multiplier based on Adiabatic Logic" in the International Journal of Innovations in Engineering and Technology(IJIET).

[7]A.Kramer,J.S.Denker,B.Flower,andJ.Moroney'spaper titled"2ndorderadiabaticcomputationwith2N-2Pand2N2N2P logic circuits" appeared in the proceedings of the InternationalSymposiumonLowPowerDesign(ISLPED).

[8] Electronics Letters, "Positive Feedback in Aadiabatic Logic,"byA.Vetuli,S.DiPascoli,andL.M.Reyneri.